Giuliano Donzellini Luca Oneto Domenico Ponta Davide Anguita

# Introduction to Digital Systems Design

# Introduction to Digital Systems Design

Giuliano Donzellini · Luca Oneto Domenico Ponta · Davide Anguita

# Introduction to Digital Systems Design

Giuliano Donzellini Dipartimento di Ingegneria Navale, Elettrica, Elettronica e delle Telecomunicazioni (DITEN) Università degli Studi di Genova

Genoa Italy

e-mail: giuliano.donzellini@unige.it

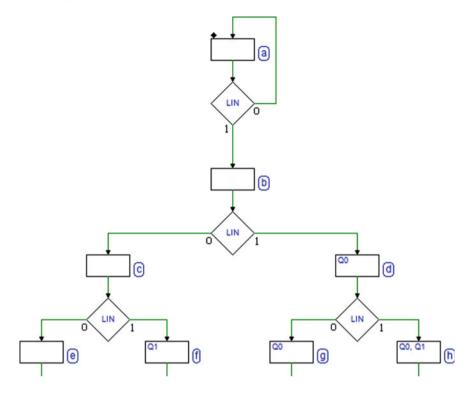

Luca Oneto

Department of Informatics, Bioengineering,

Robotics and Systems Engineering

(DIBRIS)

Università degli Studi di Genova

Genoa Italy

e-mail: luca.oneto@unige.it

Domenico Ponta Università degli Studi di Genova Genoa Italy

e-mail: ponta@unige.it

Davide Anguita

Department of Informatics, Bioengineering,

Robotics and Systems Engineering

(DIBRIS)

Università degli Studi di Genova Genoa

Italy

e-mail: davide.anguita@unige.it

ISBN 978-3-319-92803-6 ISBN 978-3-319-92804-3 (eBook) https://doi.org/10.1007/978-3-319-92804-3

Library of Congress Control Number: 2018943258

Originally published in Italian as "Introduzione al Progetto di Sistemi Digitali", in 2018 by Springer Milano, Italy, Print ISBN 978-88-470-3962-9, Online ISBN 978-88-470-3963-6. The rights for the Italian language version of the text are owned by Springer-Verlag Italia S.r.l. 2018.

© Springer International Publishing AG, part of Springer Nature 2019

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by the registered company Springer International Publishing AG part of Springer Nature

The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

To my wife Melina and my sons Sara and Paolo, who supported me with their love in this work, leaving me all the necessary time often subtracted to their needs.

To my Father and my Mother, who I did not have time to thank as I would have liked.

Giuliano Donzellini

To my Mom and Dad for my absences.

To Federica for her presence.

Luca Oneto

To my wife Luisa for the gift of her time and the lifelong encouragement and support.

To the memory of Sandro Chiabrera, teacher, mentor and friend.

Domenico Ponta

Dedicated to Sandro Ridella, my mentor and friend who, after all of these years, never stops teaching me. Davide Anguita

# Foreword of Prof. Filippo Sorbello

It is a great pleasure to present the book *Introduction to Digital Systems Design* by my friends and colleagues Donzellini, Oneto, Ponta, and Anguita. This textbook is suited for first year students of Engineering and Computer Science. It starts from the theoretical bases of digital systems, chosen and treated at the right level of depth, proceeds toward the analysis and synthesis of combinational and sequential logic to reach its target of designing and simulating controller–datapath systems. A very high number of examples and exercises with related solutions are provided.

The evolution of electronic technologies has brought a wide diffusion of digital systems in every field of everyday life. Speed, density, and complexity of current digital circuits have been made possible by automatic design methodologies and technological progress.

The knowledge of the theoretical bases of logic networks is necessary to achieve a complete mastery of digital system architectures of different complexities and also for the correct use of automatic design tools based on hardware description languages (HDLs).

First year students possess neither the adequate programming and abstraction abilities nor the physics and electronics knowledge necessary to use HDLs properly. In this textbook, this difficulty is overcome by employing a simulation tool (*Deeds*), developed by one of the authors, which uses an user-friendly interface. *Deeds* is employed to simulate the behavior both of the circuits proposed in the textbook and of those that the learner will autonomously design and then verify. *Deeds* projects can be exported in HDL and tested on FPGA circuits.

The use of languages for hardware description, together with the knowledge of the theoretical bases of logic circuits, represent the keys to understanding the digital world.

I think that this book is a good tool to face this challenge, given the ability that the authors have shown in transferring the necessary theoretical and professional know-how in a text with clear contents, smooth layout, and pleasant aspect.

Palermo, Italy March 2018 Filippo Sorbello

### Foreword of Prof. Mauro Olivieri

The textbook written by Giuliano Donzellini, Luca Oneto, Domenico Ponta, and Davide Anguita is characterized by two features that distinguish it in the wide field of university textbooks introducing digital design.

The first feature is the focus on a well-defined group of notions and tools representing the basis for digital systems: combinational and sequential logic synthesis and the topics strictly connected with them. The book covers neither electronic circuits nor microprocessor systems, and by remaining within these limits, it allows great clarity, precision, completeness, and consistency for the learners, as it appears immediately to the reader by inspecting the high number of schematics and timing diagrams provided with the textbook. Besides, the availability of solved exercises, together with the simulation software *Deeds*, represents a key element that is always appreciated and requested by students.

The second feature is the balance between the theoretical structure and the practical implementation, which allows solid learning. Even though in the textbook the word "voltage" is never cited, a student using the book always has the impression he/she is studying an electronic system formalization. At the same time, the textbook avoids presenting the topics only as a series of practical design examples without a theoretical basis.

This peculiarity characterizes the approach of the "school" of digital systems at the University of Genoa, in respect of which I consider myself an outsider.

For these reasons, the textbook of Donzellini, Oneto, Ponta, and Anguita is a precious tool for a student willing to deeply understand the concepts belonging to the big world of digital electronics design.

Roma, Italy March 2018 Prof. Mauro Olivieri

### **Preface**

The large and ever-growing complexity of today's digital systems places heavy demands on educational systems that are in charge of training the new generations of designers or just providing a solid understanding of the digital world. Academic institutions struggle to keep the pace of technological advancements, and people, like the authors of this book, who are in charge of introductory- or intermediate-level education, have the responsibility to face the problem and make choices.

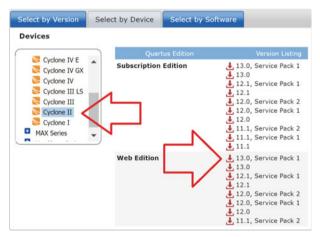

It is certainly obvious that a digital designer must be trained in the use of hardware description languages (HDLs) and it is nowadays a common practice to introduce them very early in the courses, substituting the traditional approach based on components and schematics. The choice to describe digital systems by HDL matches very well with the adoption of Field-Programmable Gate Arrays (FPGA) for the practical implementation of projects, using prototype boards provided by chip producers.

Nevertheless, it is our opinion that the adoption of HDL in a beginner course of logic networks with limited resources in terms of credits (as in our case) may present problems. We believe that it is not easy to build a solid understanding of the foundations by completely replacing logic components and schematics with HDL, which requires a level of abstraction and a familiarity with programming that beginner students generally do not possess.

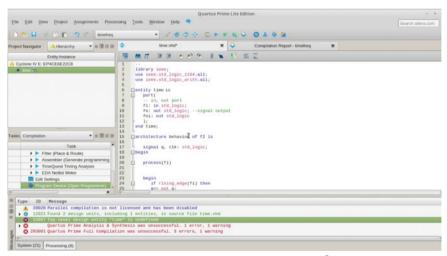

What is more, employing a simulation and synthesis software developed by FPGA chip producers presents other problems. Tools developed for digital systems designers may not necessarily satisfy learning needs: their use is not immediate for students, who may end up using them partially and mechanically, with the risk of missing important basic concepts, hidden under the technicalities of HDL and tools.

It is therefore necessary that students acquire a solid foundation on which to build design abilities and, at the same time, adapt to the fast rate of technological innovation, while gaining familiarity with languages and design tools.

For these reasons, the textbook maintains a traditional approach to logic networks, described and designed through symbols and schematics, while taking into account today's state of the art when choosing topics and, especially, exercises and

xii Preface

projects. This feature allows an optimal use of the book in university curricula that contain only one course on digital hardware, while providing a solid foundation for higher-level studies.

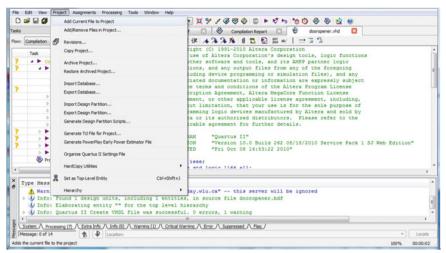

The book takes an original approach in introducing FPGA devices and VHDLs. The last chapter shows how projects similar to the ones presented earlier and tested by simulation only can be practically and quickly implemented on FPGA boards, using Deeds tools. The procedure offers the opportunity of an "hands-on" introduction to FPGA devices and VHDL.

The book is self-sufficient, since it supports the theoretical part with a huge number of examples and exercises, complete with their solutions. In courses that have room for a laboratory session, the symbiosis with the *Digital Electronics Education and Design Suite* (*Deeds*) simulation tool can be exploited, with important advantages. *Deeds* was developed recently by one of the authors (Giuliano Donzellini), with the precise target of supporting learning and laboratory activities for Information Engineering students. The strong connection with *Deeds* represents an important strength and the originality of our work, since all the schematics, examples, and design exercises included, from the easiest to the most complex, were created with *Deeds* and are available online for an immediate simulation.

The *Deeds* environment covers all the principal aspects of digital systems design, from combinational and sequential logic to finite state machines and embedded systems, thus allowing for the design and simulation of complex networks containing standard logic, finite state machines, user-defined components, and microprocessors, including their programming in *assembly* language.

*Deeds* has been developed with the idea of matching ease of use and almost professional features. The main differences between *Deeds* and a professional tool are represented by the friendliness of the user interface and the availability of a wide collection of teaching material and projects. Furthermore, *Deeds* is an "alive," continuously evolving system: updates are periodically available to improve existent tools and add new ones. The same is true for teaching materials.

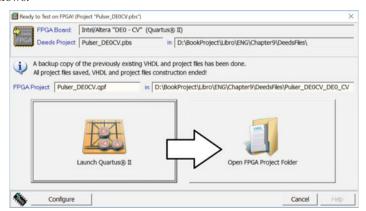

The transition toward FPGA devices is supported by *Deeds* that allows to export any of its projects to a professional tool, in order to test it in FPGA hardware. *Deeds* bypasses the complexity of the process that is normally required by a specific professional software and does not require writing HDL code, which is automatically generated by *Deeds*. The rich teaching material of *Deeds* is hence redirected toward FPGA implementation, without substantial modifications.

However, after practicing with the automatic HDL code generation by *Deeds*, students can directly interact with FPGA tools, thus having the possibility to observe, modify, and reuse HDL code (VHDL in our case), making a gradual transition toward current design techniques.

Preface xiii

### **Teaching Objectives**

According to authors' experience, the whole content of the book, together with design exercises and simulations based on *Deeds*, may be developed in an introductory course to digital systems of at least nine credits.

In the following, we briefly report the content of the chapters, indicating in italics the topics that can be avoided without loss of continuity with the teaching project, for courses with a smaller number of credits:

### 1. Boolean Algebra and Combinational Logic

Classic approach that does not require preliminary knowledge.

It is possible to skip Shannon's theorems.

### 2. Combinational Network Design

- Synthesis and minimization with Karnaugh maps.

- Standard combinational logic.

- Propagation delays.

Variable-Entered Maps and hazards may be omitted.

### 3. Numeral Systems and Binary Arithmetic

- Classic approach.

- Arithmetic networks.

Binary negative numbers may be omitted, as well as BCD arithmetic.

### 4. Complements in Combinational Network Design

Minimization of expressions with Quine–McCluskey method.

The entire chapter may be omitted.

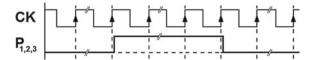

### 5. Introduction to Sequential Networks

- Intuitive transition from combinational to sequential logic.

- Structure and operation of principal flip-flop types.

- Dynamic flip-flop characteristics.

It is possible to consider just "D" and "E" logic types and to skip their circuital details.

### 6. Flip-Flop-BasedSynchronous Networks

- Introduction to synchronous flip-flop networks.

- Sequential networks: registers and counters.

- Techniques for timing analysis of synchronous networks.

Counters and registers section may be reduced, as well as timing analysis of sequential networks.

Preface

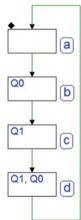

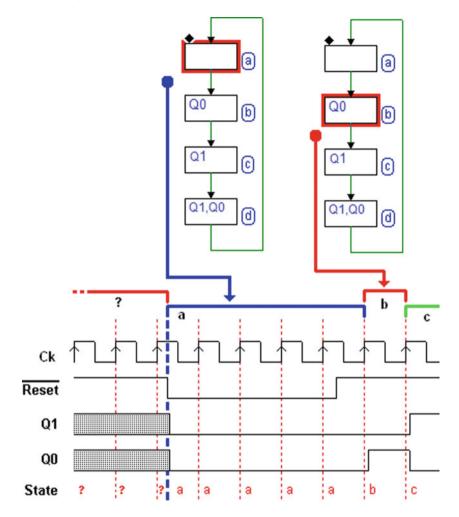

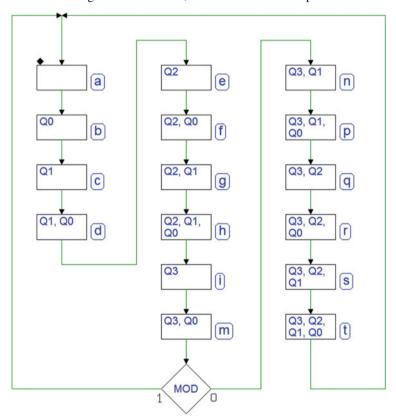

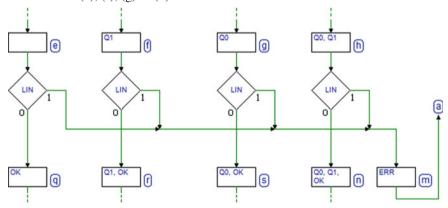

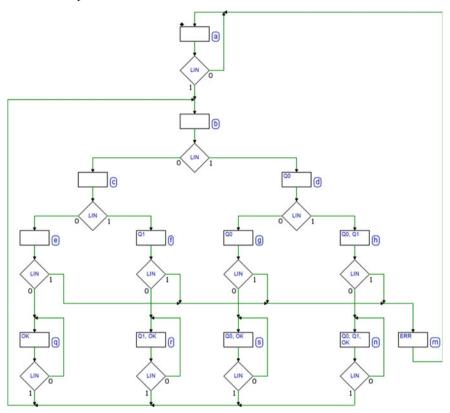

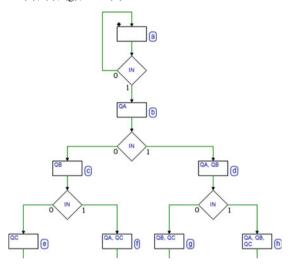

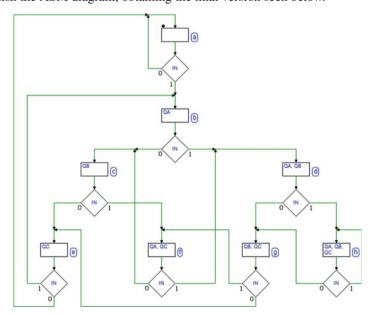

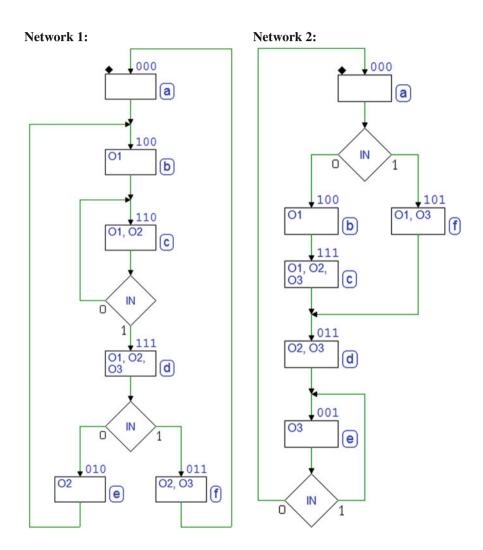

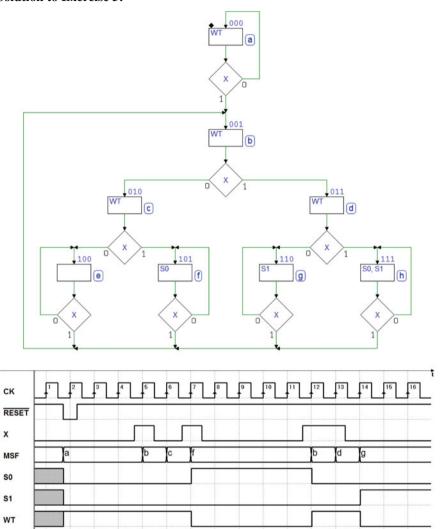

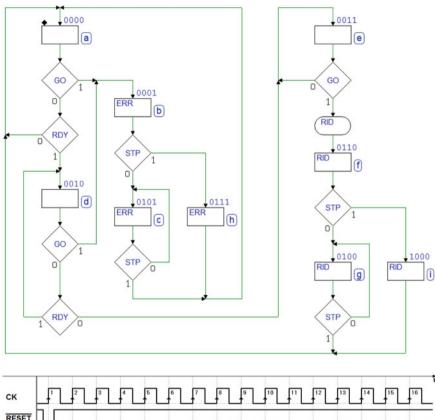

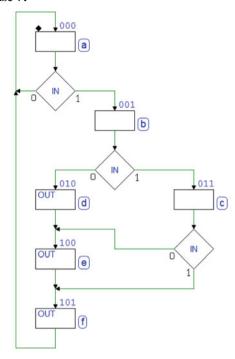

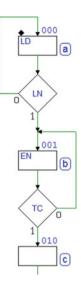

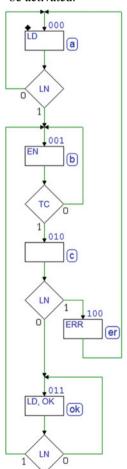

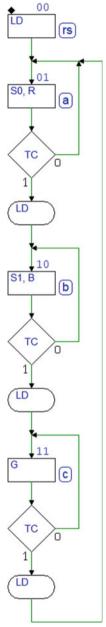

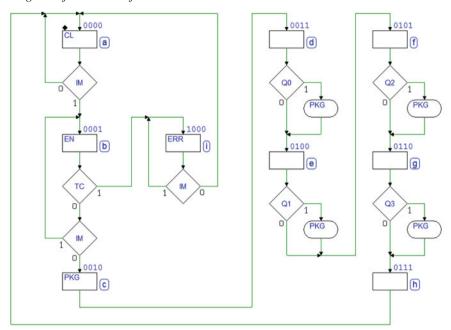

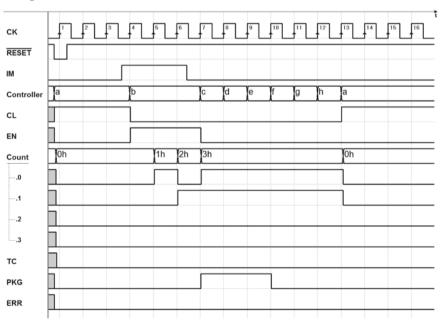

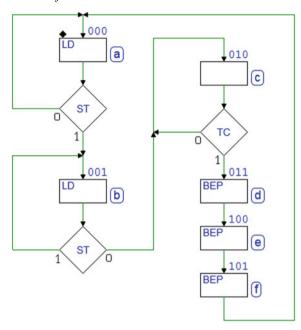

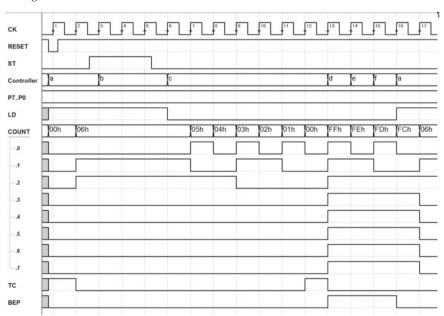

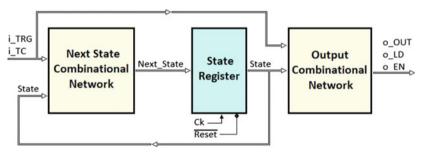

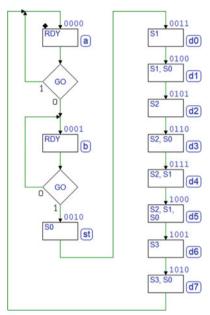

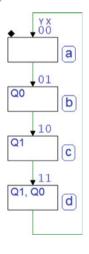

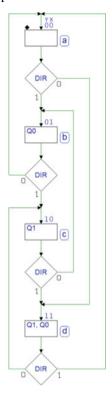

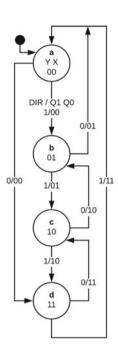

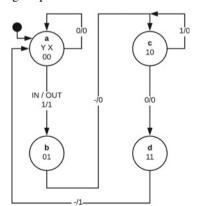

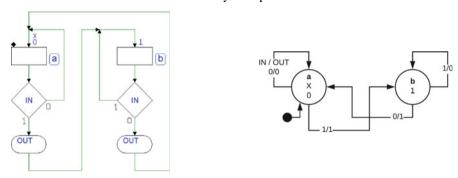

### 7. Sequential Networks as Finite State Machines

- FSM project, realized through ASM diagrams.

- Solved exercises of ASM diagrams.

- FSM synthesis with state tables and maps.

FSM synthesis may be reduced, by omitting variable-entered maps, or completely left aside.

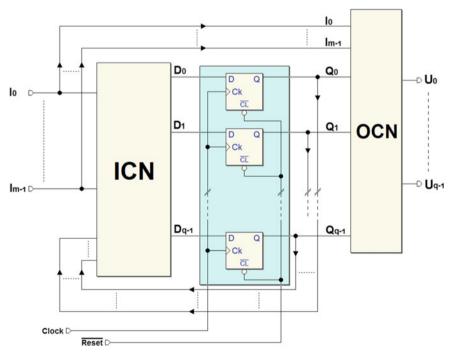

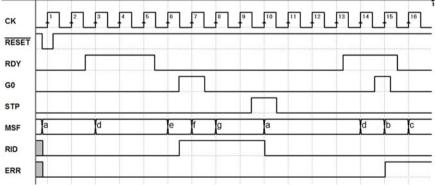

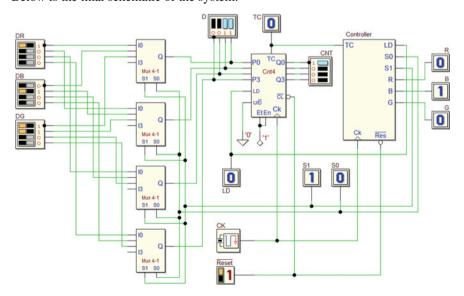

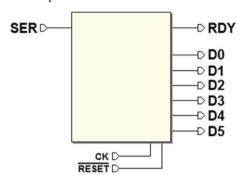

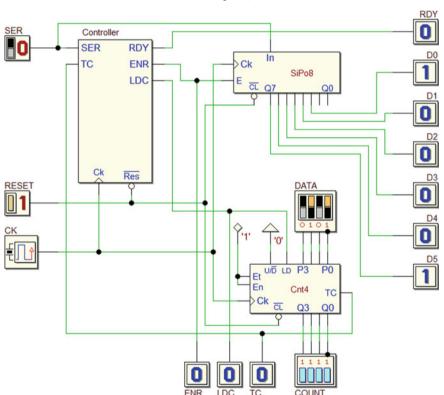

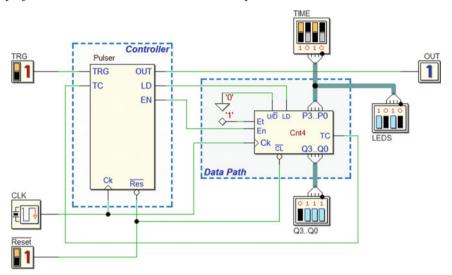

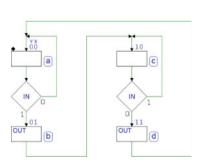

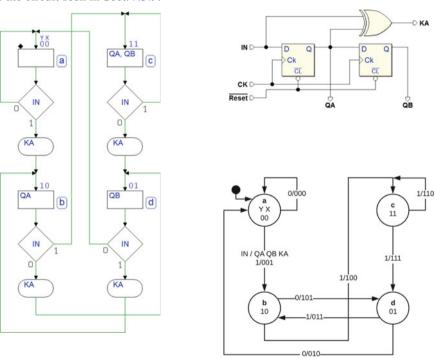

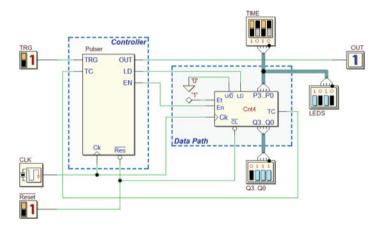

### 8. The Finite State Machine as System Controller

- Design of Controller–Datapath systems.

- Solved exercises on controller-datapath systems.

This chapter applies all the material presented in the book to develop controller-datapath systems. The projects may be chosen according to the needs and level of the class.

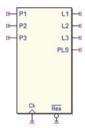

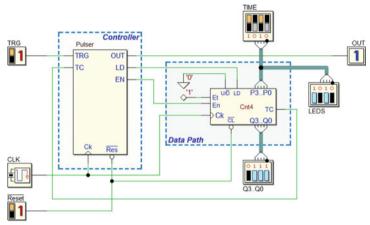

### 9. Introduction to FPGA and HDL Design

- Introduction to FPGA.

- System prototyping on FPGA with *Deeds* tools.

- Introduction to VHDL.

- Examples of FPGA prototyping projects.

This chapter requires the use of Deeds, and it is fully exploited when accompanied by laboratory activities.

### How to Use the Book

The strict connection between this book and the *Deeds* tool suggests using it together with the simulation tools, both to verify and test concepts and procedures in an active way and to have a support for the solution of the exercises and the design of systems.

This "learning by doing" practice allows students to progressively build the analytic and design capabilities that represent the target to reach.

Giuliano Donzellini Luca Oneto Domenico Ponta Davide Anguita Genova, Italy

# **Digital Contents for the Book**

This textbook contains theoretical parts, examples, exercises, and solutions. All the examples have also been implemented with the *Deeds* simulator that can be downloaded from the link:

### https://www.digitalelectronicsdeeds.com

The Web site contains a description of the *Deeds*'s features, tutorials, and learning materials. The simulator does not require an Internet connection.

On the same Web site, as additional material, it is possible to find almost all the schematics and charts included in the book:

### https://www.digitalelectronicsdeeds.com/books

Thanks to this material, it is possible to simulate with *Deeds* the proposed circuits and the exercises. The material has been organized by following the same structure of the book in order to make it easier to access. On the same Web site, future updates, corrections, and additions will be made available.

# **Contents**

| l | Boole | ean Algebra and Combinational Logic                       | 1 |

|---|-------|-----------------------------------------------------------|---|

|   | 1.1   | Analog and Discrete Variables                             | 1 |

|   | 1.2   | Boolean Variables                                         | 3 |

|   | 1.3   | Boolean Functions                                         | 4 |

|   | 1.4   | Truth Tables                                              | 4 |

|   | 1.5   | Definition of Boolean Algebra                             | 5 |

|   | 1.6   | The Fundamental Properties of Boolean Algebra             | 6 |

|   | 1.7   | Other Operations                                          | 0 |

|   | 1.8   | Functionally Complete Operation Sets                      | 1 |

|   | 1.9   | Shannon's Expansion Theorem                               | 4 |

|   | 1.10  | Level of Boolean Expressions                              | 7 |

|   | 1.11  | Literals                                                  | 7 |

|   | 1.12  | Minterms                                                  | 8 |

|   | 1.13  | Maxterms                                                  | 8 |

|   | 1.14  | Implicants                                                | 8 |

|   | 1.15  | Prime Implicants                                          | 8 |

|   | 1.16  | Combinational Networks                                    | 9 |

|   |       | 1.16.1 Example: Logical Network Analysis                  | 9 |

|   |       | 1.16.2 Example: Two-Level Logical Network Analysis 20     | 0 |

|   |       | 1.16.3 Example: Circuit Schematic of a Logical            |   |

|   |       | Network (1)                                               | 0 |

|   |       | 1.16.4 Example: Circuit Schematic of a Logical            |   |

|   |       | Network (2)                                               | 1 |

|   |       | 1.16.5 Example: Defining the Behavior of a Logical        |   |

|   |       | Network                                                   | 1 |

|   |       | 1.16.6 Example: Circuit Schematic from the Truth Table 22 | 2 |

|   |       | 1.16.7 Example: Controlling a Heating System              | 3 |

|   |       | 1.16.8 Example: Two Channels Multiplexer (Selector) 24    | 4 |

xviii Contents

|                               | 1.17                      | Exercises                                                                                                      |          |  |  |  |  |

|-------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

|                               | 1.18                      | Solutions                                                                                                      | 29       |  |  |  |  |

| 2                             | Coml                      | binational Network Design                                                                                      | 33       |  |  |  |  |

| _                             | 2.1                       |                                                                                                                | 33       |  |  |  |  |

|                               | 2.2                       |                                                                                                                | 36       |  |  |  |  |

|                               | 2.2                       | $\mathcal{C}$                                                                                                  | 38       |  |  |  |  |

|                               |                           |                                                                                                                | 41       |  |  |  |  |

|                               |                           |                                                                                                                | 41       |  |  |  |  |

|                               |                           | ±                                                                                                              | 42       |  |  |  |  |

|                               | 2.3                       |                                                                                                                | 45       |  |  |  |  |

|                               | 2.5                       | •                                                                                                              | 46       |  |  |  |  |

|                               | 2.4                       | $\mathcal{E}$                                                                                                  | 46       |  |  |  |  |

|                               | 2.5                       | •                                                                                                              | 47       |  |  |  |  |

|                               | 2.6                       | •                                                                                                              | 48       |  |  |  |  |

|                               | 2.0                       |                                                                                                                | 48       |  |  |  |  |

|                               |                           |                                                                                                                | 51       |  |  |  |  |

|                               |                           | 1                                                                                                              | 53       |  |  |  |  |

|                               |                           | 1                                                                                                              | 55       |  |  |  |  |

|                               |                           |                                                                                                                | 57       |  |  |  |  |

|                               |                           | 2.6.6 Using Multiplexers to Synthesize Combinational                                                           | 51       |  |  |  |  |

|                               |                           |                                                                                                                | 58       |  |  |  |  |

|                               | 2.7 Variable-Entered Maps |                                                                                                                |          |  |  |  |  |

|                               | 2.7                       | 1                                                                                                              | 60<br>60 |  |  |  |  |

|                               |                           | 5 & 1                                                                                                          | 63       |  |  |  |  |

|                               | 2.8                       |                                                                                                                | 64       |  |  |  |  |

|                               | 2.0                       |                                                                                                                | 64       |  |  |  |  |

|                               |                           |                                                                                                                | 66       |  |  |  |  |

|                               |                           | 2.8.3 Elimination of Static Hazards                                                                            | 67       |  |  |  |  |

|                               |                           | 2.8.4 Notes on Eliminating Hazards                                                                             | 70       |  |  |  |  |

|                               | 2.9                       |                                                                                                                | 70       |  |  |  |  |

|                               | 2.9                       |                                                                                                                | 70       |  |  |  |  |

|                               |                           | I .                                                                                                            | 72       |  |  |  |  |

|                               | 2.10                      |                                                                                                                | 73       |  |  |  |  |

|                               | 2.10                      |                                                                                                                | 73       |  |  |  |  |

|                               |                           |                                                                                                                | 77       |  |  |  |  |

| •                             |                           |                                                                                                                |          |  |  |  |  |

| 3                             |                           | · ·                                                                                                            | 79       |  |  |  |  |

|                               | 3.1                       | , and the second se | 79       |  |  |  |  |

|                               | 3.2                       | Binary Numbering System (BIN)                                                                                  | 80       |  |  |  |  |

|                               |                           | 3.2.1 Converting from Binary System to Decimal                                                                 | 80       |  |  |  |  |

|                               |                           |                                                                                                                | 81       |  |  |  |  |

|                               | 2.2                       | 1                                                                                                              | 82<br>83 |  |  |  |  |

| 3.3 Octal Number System (OCT) |                           |                                                                                                                |          |  |  |  |  |

Contents xix

|   | 3.4  | Hexade   | cimal Number System (HEX)                         | 84  |

|---|------|----------|---------------------------------------------------|-----|

|   | 3.5  | Others   | Binary Codes                                      | 85  |

|   |      | 3.5.1    | Binary Coded Decimal                              | 85  |

|   |      | 3.5.2    | GRAY Codes                                        | 86  |

|   | 3.6  | Binary   | Arithmetic                                        | 87  |

|   |      | 3.6.1    | Addition                                          | 87  |

|   |      | 3.6.2    | Subtraction                                       | 88  |

|   |      | 3.6.3    | Products                                          | 89  |

|   | 3.7  | BCD 8    | 421 Arithmetic                                    | 89  |

|   | 3.8  | Binary   | Rational Numbers                                  | 91  |

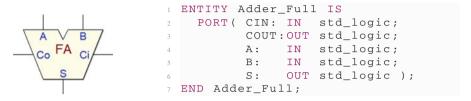

|   | 3.9  | Arithme  | etic Networks                                     | 91  |

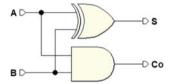

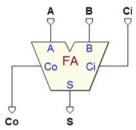

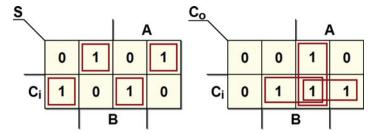

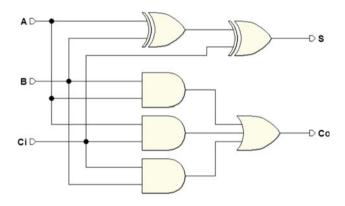

|   |      | 3.9.1    | Half Adders                                       | 91  |

|   |      | 3.9.2    | Full Adders                                       | 92  |

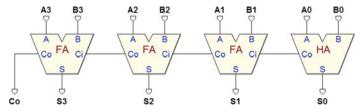

|   |      | 3.9.3    | Ripple Carry Adder                                | 93  |

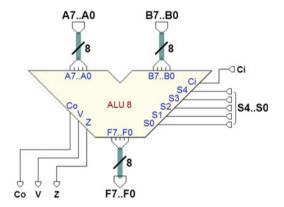

|   |      | 3.9.4    | Arithmetic Logic Unit (ALU)                       | 94  |

|   | 3.10 | Relative | e Numbers in Binary                               | 95  |

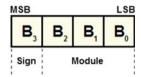

|   |      | 3.10.1   | Representation in "Module and Sign" Code          | 95  |

|   |      | 3.10.2   | Complementation                                   | 97  |

|   |      | 3.10.3   | Representation in "Ones' Complement" Code         | 99  |

|   |      | 3.10.4   | Representation in "Two's Complement" Code         | 101 |

|   |      | 3.10.5   | Sign Extension                                    | 102 |

|   | 3.11 | Represe  | entation of Real Numbers                          | 103 |

|   | 3.12 | Alphan   | umeric Codes                                      | 104 |

|   | 3.13 | Error D  | Detection Codes: Parity Generator and Checker     | 106 |

|   | 3.14 | Exercis  | es                                                | 108 |

|   |      | 3.14.1   | Binary Numbers                                    | 108 |

|   |      | 3.14.2   | Signed Binary Numbers                             | 108 |

|   |      | 3.14.3   | Octal and Hexadecimal Numbers                     | 109 |

|   | 3.15 | Solution | ns                                                | 109 |

|   |      | 3.15.1   | Binary Numbers                                    | 109 |

|   |      | 3.15.2   | Signed Binary Numbers                             | 111 |

|   |      | 3.15.3   | Octal and Hexadecimal Numbers                     | 112 |

| 4 | Comp | olements | in Combinational Network Design                   | 115 |

|   | 4.1  |          | zing Boolean Expressions with the Quine–McCluskey |     |

|   |      |          | 1                                                 | 115 |

|   |      | 4.1.1    | The Expansion Phase                               | 116 |

|   |      | 4.1.2    | The Covering Phase                                | 119 |

|   |      | 4.1.3    | Incompletely Specified Functions                  | 120 |

|   |      | 4.1.4    | Optimizing the Covering Phase                     | 120 |

|   |      | 4.1.5    | Simultaneous Optimization of Multiple Functions   | 125 |

|   |      |          |                                                   |     |

xx Contents

|   | 4.2   | Exercis        | es                                                                                            | 130 |

|---|-------|----------------|-----------------------------------------------------------------------------------------------|-----|

|   |       | 4.2.1          | Quine–McCluskey: Single Function Synthesis                                                    | 130 |

|   |       | 4.2.2          | Quine–McCluskey: Jointly Synthesis of Multiple                                                |     |

|   |       |                | Functions                                                                                     | 133 |

|   | 4.3   | Solution       | ns                                                                                            | 136 |

|   |       | 4.3.1<br>4.3.2 | Quine–McCluskey: Synthesis of a Single Function  Quine–McCluskey: Joint Synthesis of Multiple | 136 |

|   |       |                | Functions                                                                                     | 137 |

| 5 | Intro | duction        | to Sequential Networks                                                                        | 139 |

|   | 5.1   | From C         | Combinational Networks to Sequential Networks                                                 | 139 |

|   |       | 5.1.1          | Introductory Example                                                                          | 140 |

|   |       | 5.1.2          | Memorizing an Information Bit: Flip-Flops                                                     | 141 |

|   |       | 5.1.3          | Flip-Flop Classification: Logical Type and Command                                            |     |

|   |       |                | Type                                                                                          | 142 |

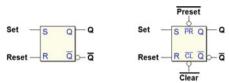

|   | 5.2   | Direct (       | Command Flip-Flops                                                                            | 143 |

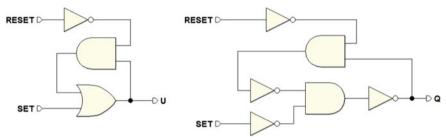

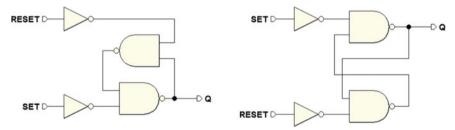

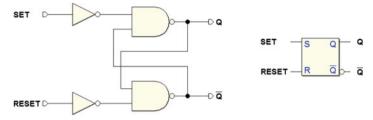

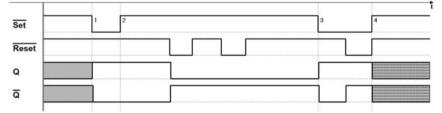

|   |       | 5.2.1          | SR Flip-Flop                                                                                  | 143 |

|   |       | 5.2.2          | D Flip-Flop                                                                                   | 147 |

|   |       | 5.2.3          | JK Flip-Flop                                                                                  | 148 |

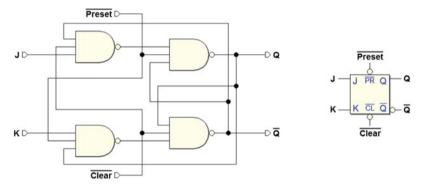

|   | 5.3   | Initializ      | zation of a Sequential Network                                                                | 149 |

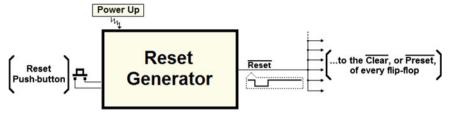

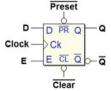

|   |       | 5.3.1          | Flip-Flop Initialization Inputs                                                               | 150 |

|   |       | 5.3.2          | Generating an Initialization Signal                                                           | 152 |

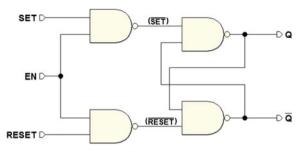

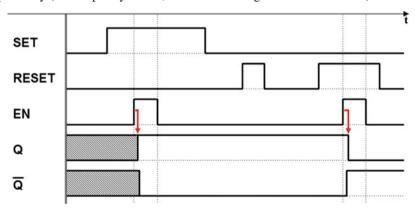

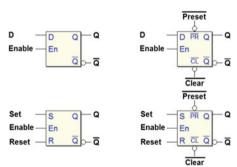

|   | 5.4   | Level-E        | Enabled Flip-Flops                                                                            | 153 |

|   |       | 5.4.1          | SR-Latch Flip-Flop                                                                            | 153 |

|   |       | 5.4.2          | D-Latch Flip-Flop                                                                             | 155 |

|   |       | 5.4.3          | JK-Latch Flip-Flop                                                                            | 156 |

|   | 5.5   | Synchro        | onization of Sequential Networks                                                              | 157 |

|   |       | 5.5.1          | The Synchronization Signal                                                                    | 157 |

|   |       | 5.5.2          | Pulse Command in Level-Enabled Flip-Flops                                                     | 158 |

|   |       | 5.5.3          | The "Clock" and the "Edge-Triggered Command"                                                  | 159 |

|   |       | 5.5.4          | Master–Slave Structure                                                                        | 160 |

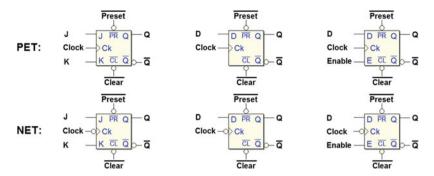

|   | 5.6   | Edge-T         | riggered Flip-Flops                                                                           | 162 |

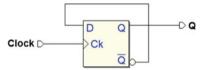

|   |       | 5.6.1          | D-PET Flip-Flop                                                                               | 162 |

|   |       | 5.6.2          | E-PET Flip-Flop                                                                               | 166 |

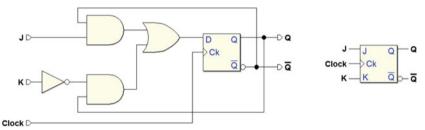

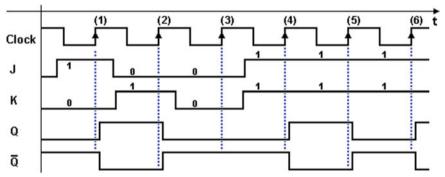

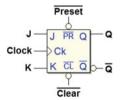

|   |       | 5.6.3          | JK-PET Flip-Flop                                                                              | 168 |

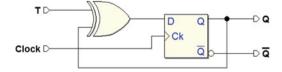

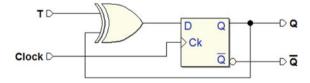

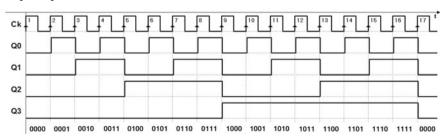

|   |       | 5.6.4          | T-PET Flip-Flop                                                                               | 170 |

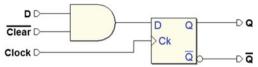

|   |       | 5.6.5          | Synchronous Initialization of Flip-Flops                                                      | 171 |

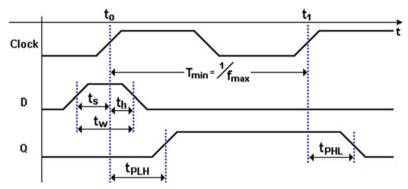

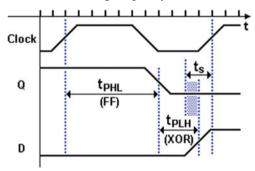

|   | 5.7   | Timing         | Parameters of Flip-Flops                                                                      | 171 |

|   |       | 5.7.1          | Relationship Between Propagation and Hold Times                                               | 172 |

|   |       | 5.7.2          | Maximum Clock Frequency of a Network                                                          |     |

|   |       |                | with Flip-Flops                                                                               | 173 |

|   | 5.8   | Flip-Flo       | ops: Graphic Symbols and Tables                                                               | 174 |

|   | -     | 5.8.1          | Logical Types                                                                                 | 174 |

|   |       |                |                                                                                               |     |

Contents xxi

|   |        | 5.8.2    | Command Types                                       | 175 |

|---|--------|----------|-----------------------------------------------------|-----|

|   |        | 5.8.3    | Excitation Tables                                   | 177 |

|   | 5.9    | Exercis  | ses                                                 | 178 |

|   | 5.10   | Solutio  | ons                                                 | 181 |

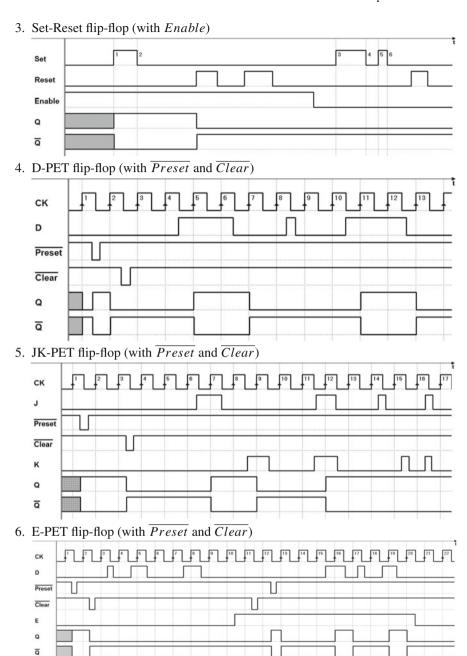

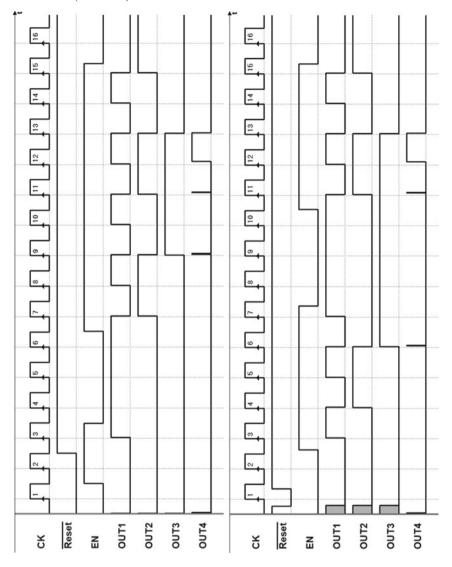

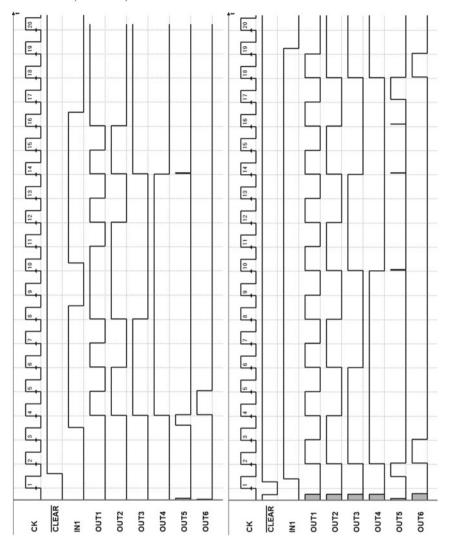

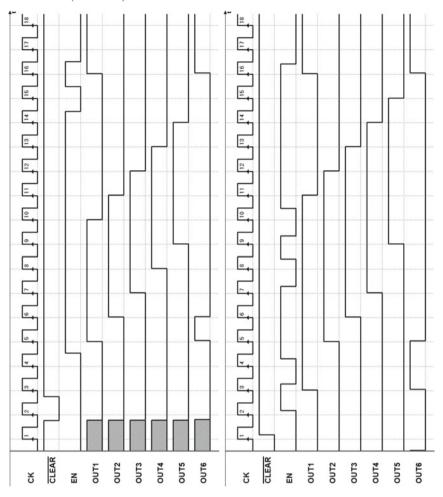

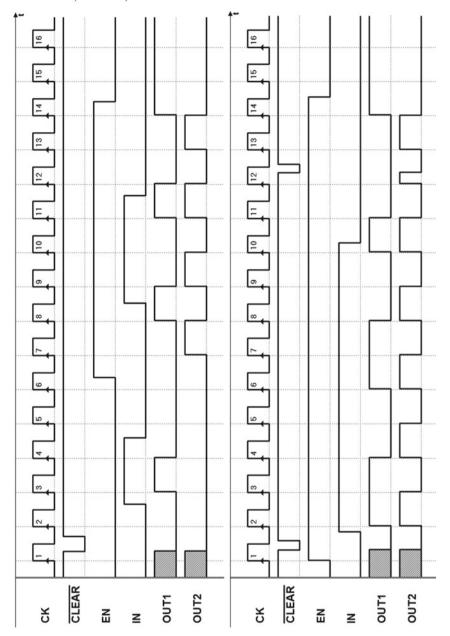

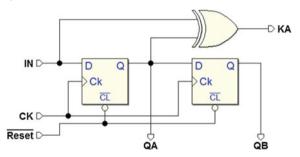

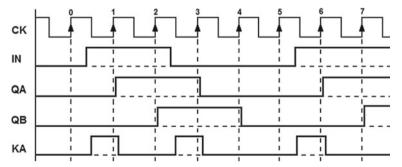

| 6 | Flip-l | Flop-Ba  | sed Synchronous Networks                            | 183 |

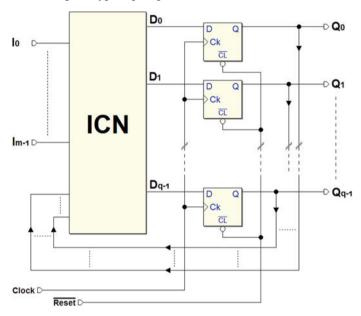

|   | 6.1    | Synchr   | onous and Asynchronous Signals                      | 185 |

|   |        | 6.1.1    | Synchronizer                                        | 186 |

|   |        | 6.1.2    | Multistage Synchronization                          | 187 |

|   | 6.2    | Registe  | ers                                                 | 188 |

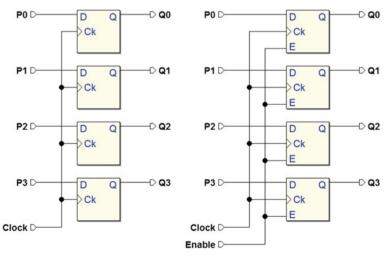

|   |        | 6.2.1    | Parallel Registers                                  | 188 |

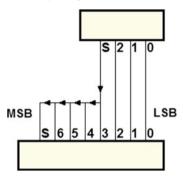

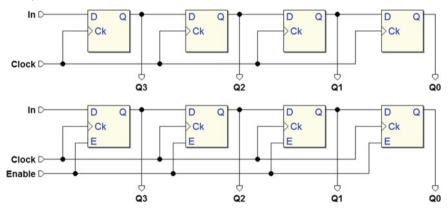

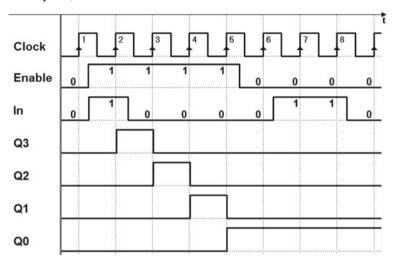

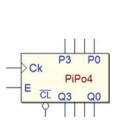

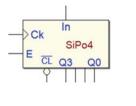

|   |        | 6.2.2    | Shift Registers                                     | 190 |

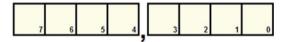

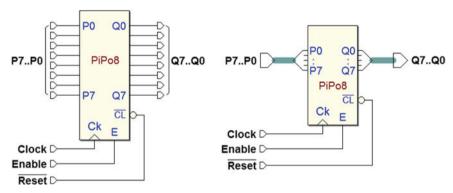

|   |        | 6.2.3    | Shift Registers with Parallel Load                  | 193 |

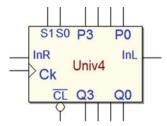

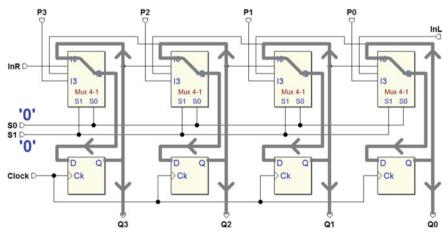

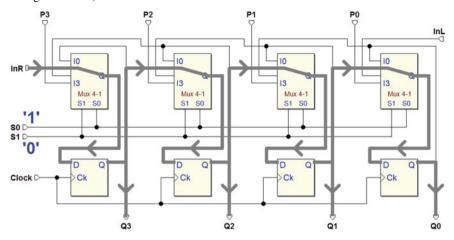

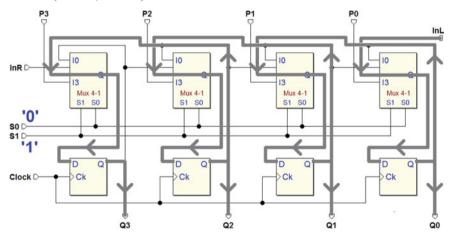

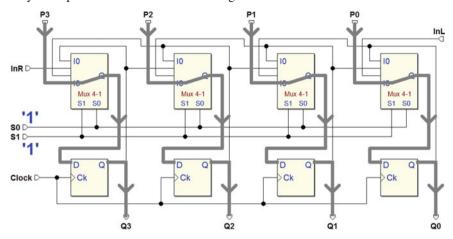

|   |        | 6.2.4    | Universal Shift Register                            | 196 |

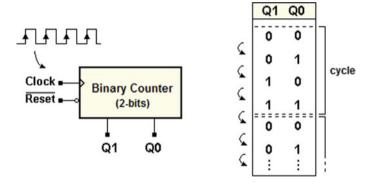

|   | 6.3    | Counte   |                                                     | 199 |

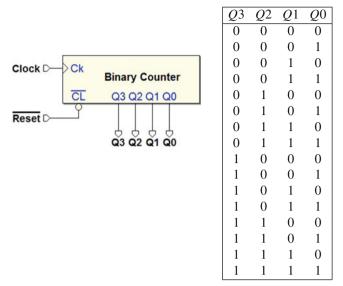

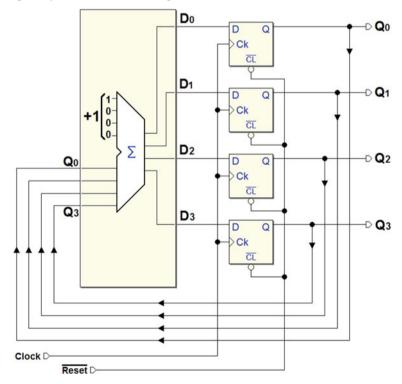

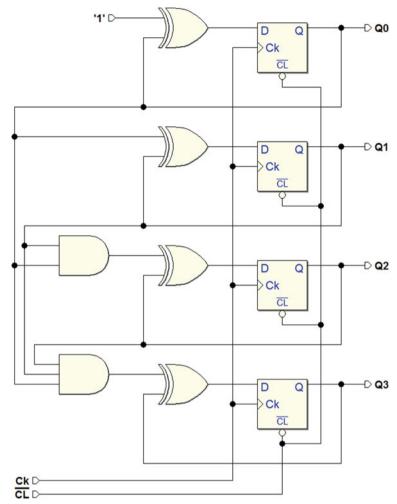

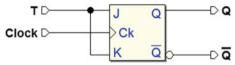

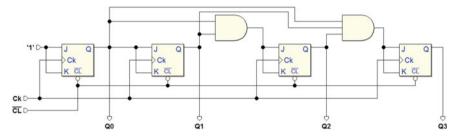

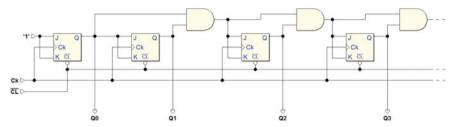

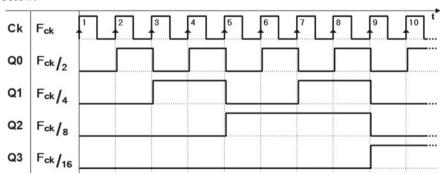

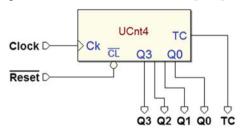

|   |        | 6.3.1    | Binary Counters                                     | 199 |

|   |        | 6.3.2    | Counters with Enabling                              | 205 |

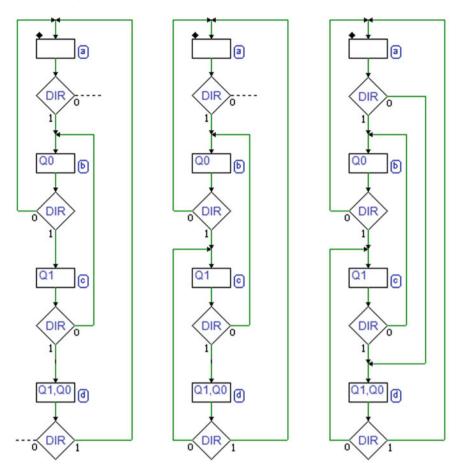

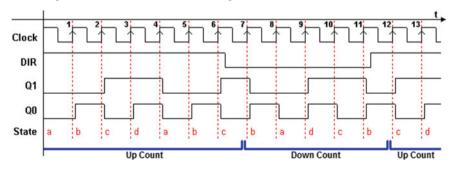

|   |        | 6.3.3    | Up/Down Counters                                    | 207 |

|   |        | 6.3.4    | "Universal" Counters                                | 210 |

|   |        | 6.3.5    | Asynchronous Counters                               | 213 |

|   | 6.4    | Netwo    | rk Analysis Examples                                | 215 |

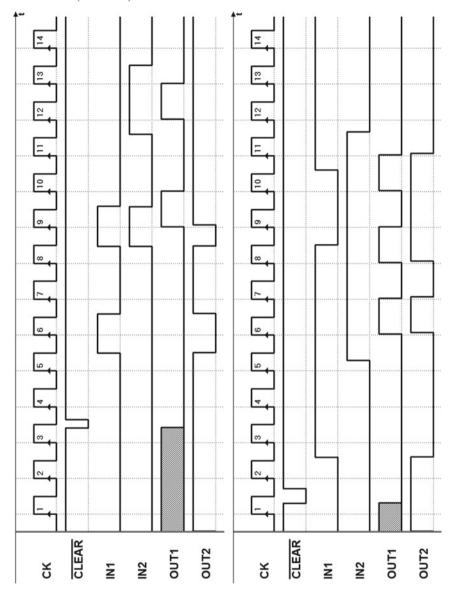

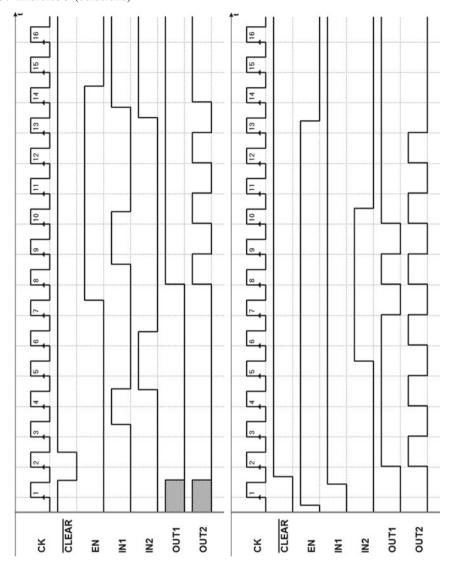

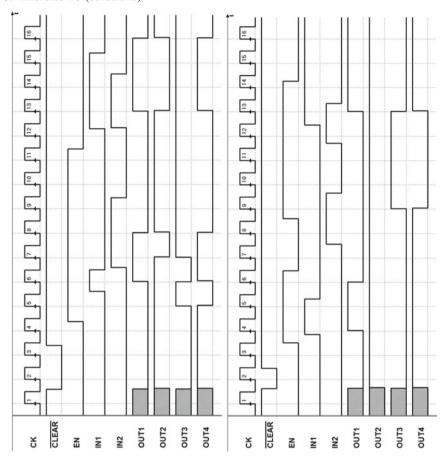

|   |        | 6.4.1    | Example 1                                           | 215 |

|   |        | 6.4.2    | Example 2                                           | 218 |

|   |        | 6.4.3    | Example 3                                           | 221 |

|   |        | 6.4.4    | Example 4                                           | 223 |

|   |        | 6.4.5    | Example 5                                           | 224 |

|   | 6.5    | Exercis  | ses                                                 | 228 |

|   | 6.6    | Solutio  | ons                                                 | 248 |

| 7 | Seque  | ential N | etworks as Finite State Machines                    | 259 |

|   | 7.1    | Finite : | State Machines: Standard Model                      | 260 |

|   |        | 7.1.1    | Synchronous and Asynchronous Machines               | 261 |

|   |        | 7.1.2    | Moore and Mealy Machines                            | 261 |

|   |        | 7.1.3    | An Example of Synchronous Finite State Machine      | 262 |

|   |        | 7.1.4    | General Equations of the Next State and the Outputs | 263 |

|   | 7.2    | ASM I    | Diagrams                                            | 265 |

|   |        | 7.2.1    | Description of States                               | 265 |

|   |        | 7.2.2    | Inputs                                              | 269 |

|   |        | 7.2.3    | Conditional Outputs                                 | 277 |

|   | 7.3    | Examp    | les of ASM Diagram Construction                     | 282 |

|   |        | 7.3.1    | Introductory Examples                               | 282 |

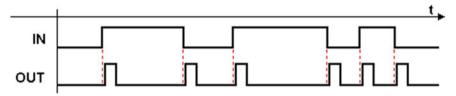

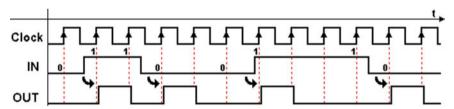

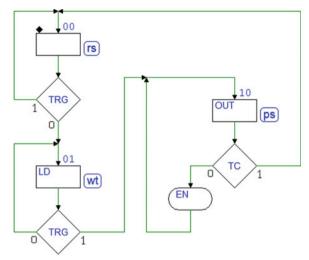

|   |        | 7.3.2    | Pulse Generators with Adjustable Duty Cycle         | 291 |

|   |        | 7.3.3    | Sequence Detector                                   | 296 |

|   |        | 7.3.4    | Serial Synchronous Transmitters (2 bits)            | 298 |

xxii Contents

|   |       | 7.3.5     | Command Receiver with Serial Synchronous Interface | 300 |

|---|-------|-----------|----------------------------------------------------|-----|

|   |       | 7.3.6     | Serial Synchronous Receiver (2 bits)               |     |

|   |       | 7.3.7     | Push-Button Handling                               |     |

|   |       | 7.3.8     | 3-Bit Shift Registers                              |     |

|   |       | 7.3.9     | Sequential Networks with Conditional Outputs       |     |

|   |       | 7.3.10    | Shift Register with XOR Tree                       |     |

|   | 7.4   |           | sis of Synchronous FSM                             |     |

|   | ,     | 7.4.1     | State Assignment                                   |     |

|   |       | 7.4.2     | Describing an FSM with a State Table               |     |

|   |       | 7.4.3     | State Table Synthesis                              |     |

|   |       | 7.4.4     | Examples of Synchronous FSM Synthesis              |     |

|   | 7.5   |           | Behavior of Synchronous FSM                        |     |

|   | ,     | 7.5.1     | FSM with no Inputs                                 |     |

|   |       | 7.5.2     | FSM with Synchronous and Asynchronous Inputs       |     |

|   |       | 7.5.3     | Synchronous Inputs                                 |     |

|   |       | 7.5.4     | Asynchronous Inputs                                |     |

|   |       | 7.5.5     | FSM Outputs (Moore's Model)                        |     |

|   |       | 7.5.6     | FSM Outputs (Mealy's Model)                        |     |

|   | 7.6   | Exercis   | ses                                                |     |

|   |       | 7.6.1     | Sequential Network Analysis in Terms of FSMs       |     |

|   |       | 7.6.2     | FSM Design Based on Textual Specifications         |     |

|   | 7.7   | Solutio   | ns                                                 |     |

|   |       | 7.7.1     | Sequential Network Analysis in Terms of FSMs       |     |

|   |       | 7.7.2     | FSM Design Based on Textual Specifications         |     |

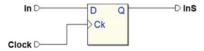

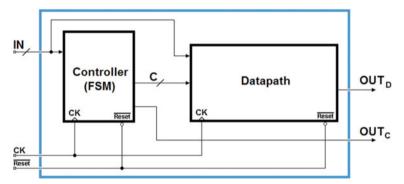

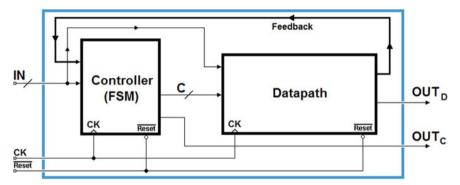

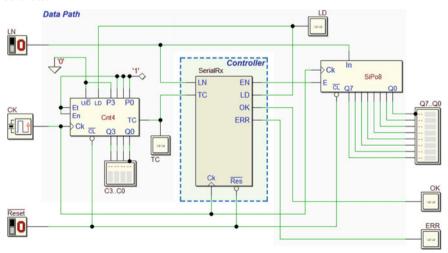

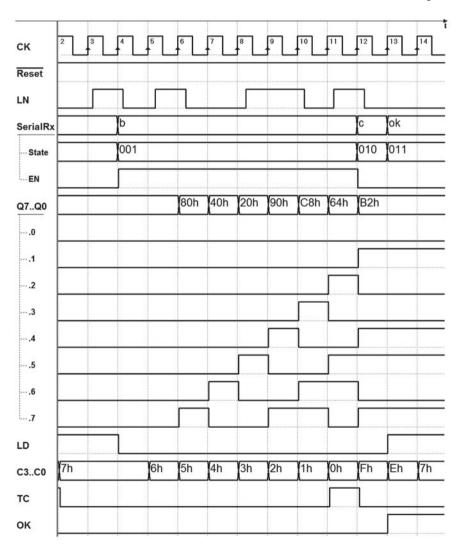

| 8 | The 1 | Finite St | ate Machine as System Controller                   | 363 |

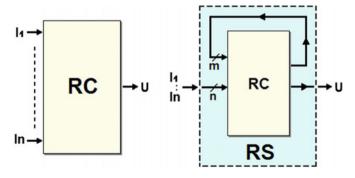

|   | 8.1   |           | Systems                                            |     |

|   | 8.2   | Open (    | Control Systems                                    | 364 |

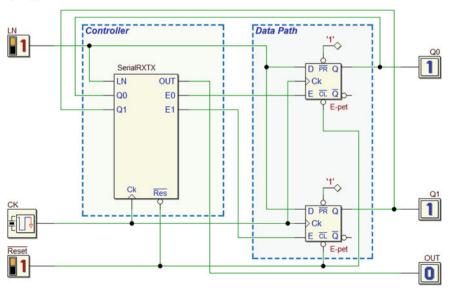

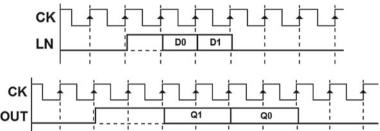

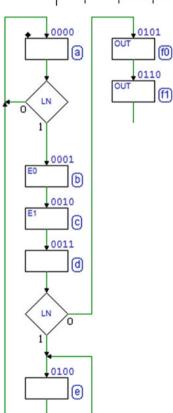

|   |       | 8.2.1     | 2-Bit Serial Receiver                              | 365 |

|   | 8.3   | Feedba    | ck Control Systems                                 | 369 |

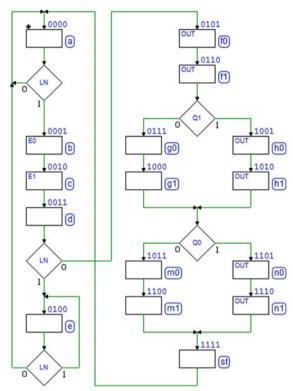

|   |       | 8.3.1     | 2-Bit Serial Receiver and Transmitter              |     |

|   |       | 8.3.2     | Pulse Generator                                    | 372 |

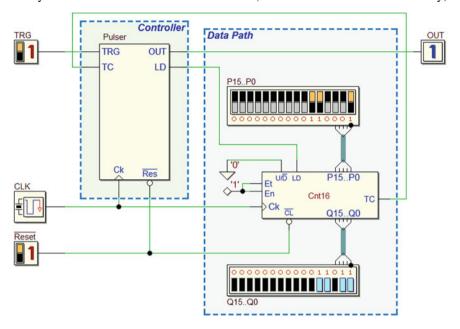

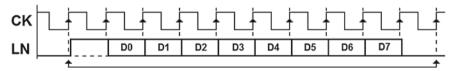

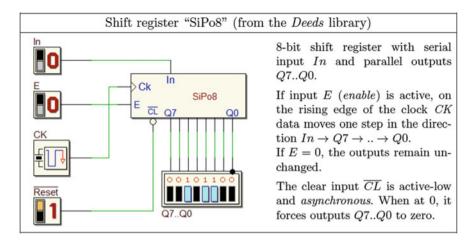

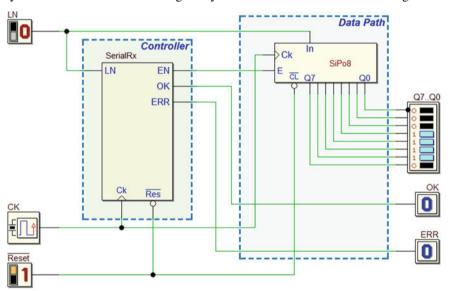

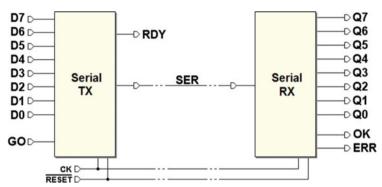

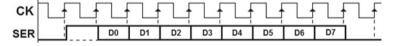

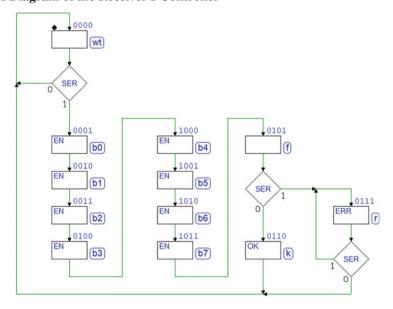

|   |       | 8.3.3     | 8-Bit Serial Receiver                              | 377 |

|   |       | 8.3.4     | Light Dimmer                                       | 384 |

|   |       | 8.3.5     | Combination Lock                                   | 388 |

|   |       | 8.3.6     | Automatic Drink Dispenser                          | 393 |

|   |       | 8.3.7     | Programmable Square Wave Generator                 |     |

|   |       | 8.3.8     | Christmas Light Systems                            | 401 |

|   | 8.4   | Design    | Exercises                                          | 405 |

|   |       | 8.4.1     | Design of the Controller of a Given Datapath       | 405 |

|   |       | 8.4.2     | Design of a Controller–Datapath System             | 424 |

Contents xxiii

|    | 8.5   | Design   | Tips                                            | 427 |

|----|-------|----------|-------------------------------------------------|-----|

|    |       | 8.5.1    | Design of a Controller–Datapath System          | 427 |

|    | 8.6   | Solution | ns                                              | 434 |

|    |       | 8.6.1    | Design of the Controller of a Given Datapath    | 434 |

|    |       | 8.6.2    | Design of a Controller–Datapath System          | 452 |

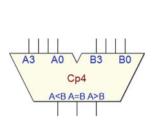

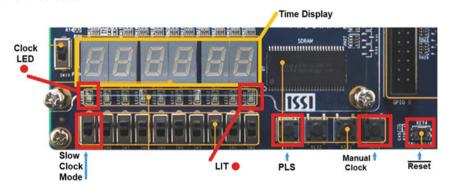

| 9  | Intro | duction  | to FPGA and HDL Design                          | 465 |

|    | 9.1   | Field-P  | rogrammable Gate Arrays                         | 465 |

|    |       | 9.1.1    | System Prototyping and FPGA                     | 466 |

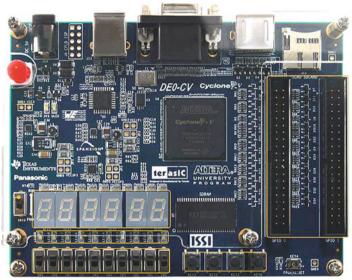

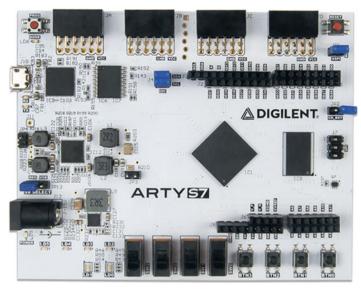

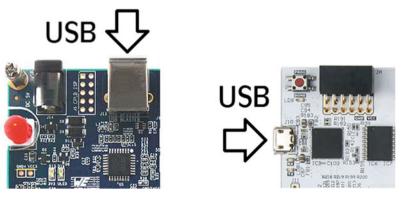

|    |       | 9.1.2    | FPGA Board Examples                             | 467 |

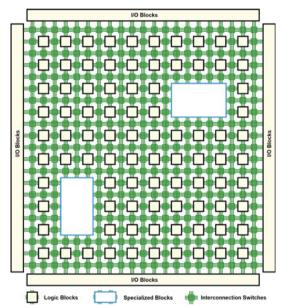

|    |       | 9.1.3    | FPGA Architecture                               | 470 |

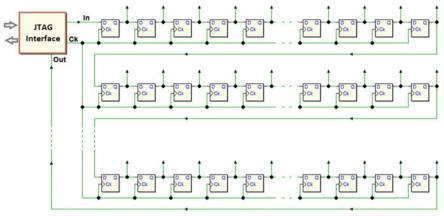

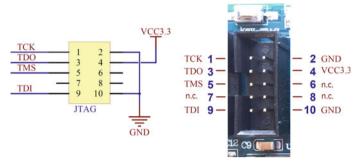

|    |       | 9.1.4    | JTAG Programming                                | 472 |

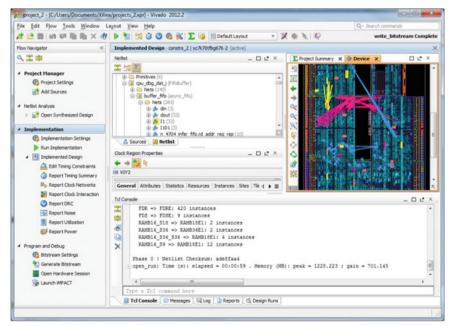

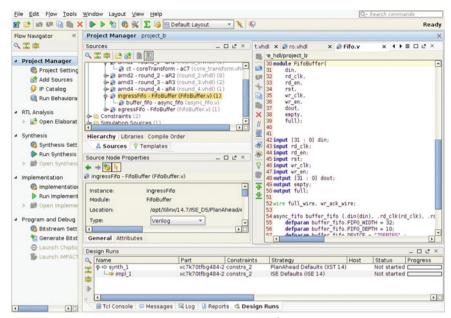

|    |       | 9.1.5    | FPGA Development Tools                          | 475 |

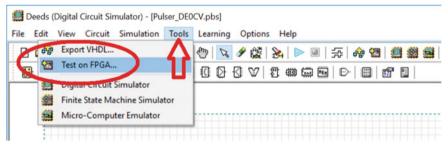

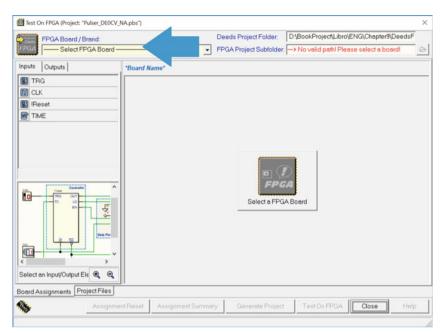

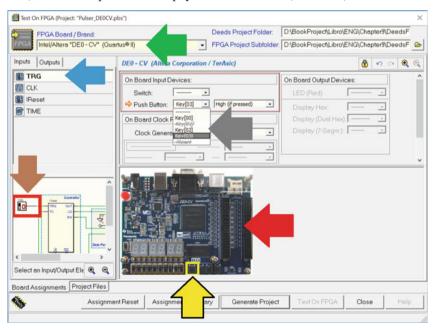

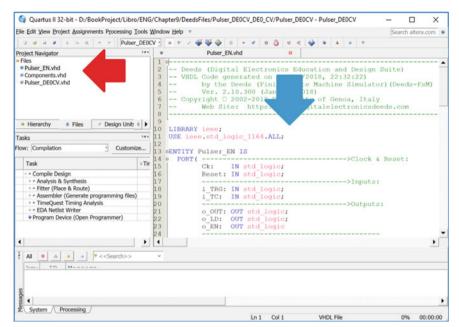

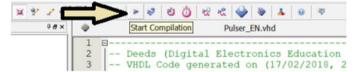

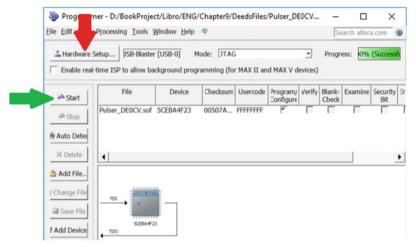

|    |       | 9.1.6    | Deeds Support for FPGA                          | 478 |

|    | 9.2   | Introdu  | ction to VHDL                                   | 485 |

|    |       | 9.2.1    | VHDL Code from Deeds                            | 486 |

|    |       | 9.2.2    | Counter                                         | 487 |

|    |       | 9.2.3    | Finite State Machine                            | 491 |

|    |       | 9.2.4    | Top-Level Entity                                | 494 |

|    |       | 9.2.5    | Other VHDL Examples                             | 497 |

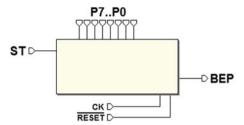

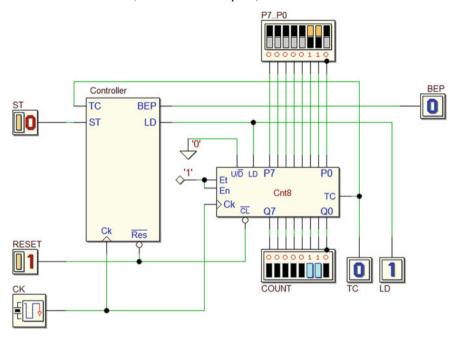

|    | 9.3   | FPGA 1   | Prototyping Exercises                           | 506 |

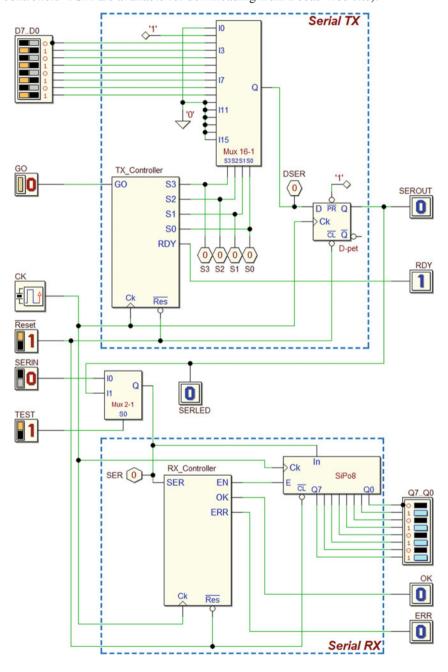

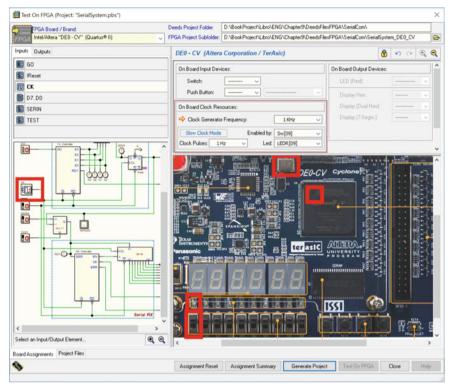

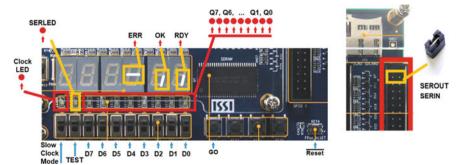

|    |       | 9.3.1    | Synchronous Serial Communication System (8-bit) | 506 |

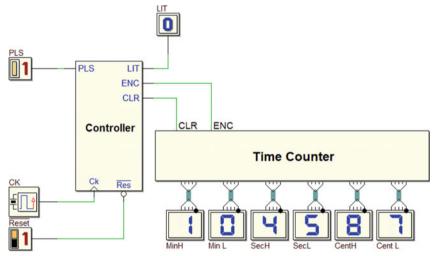

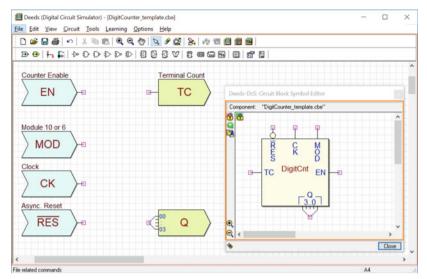

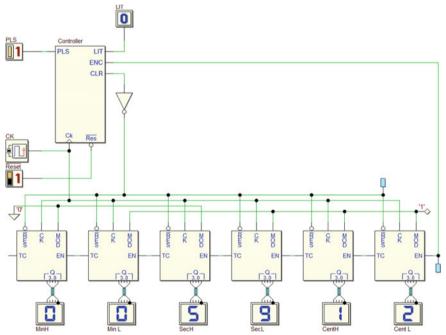

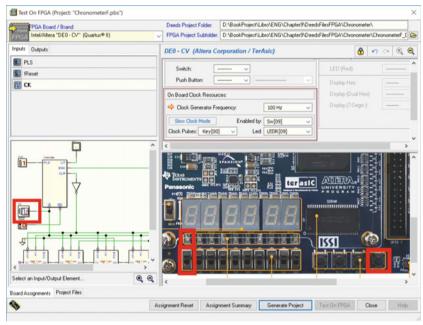

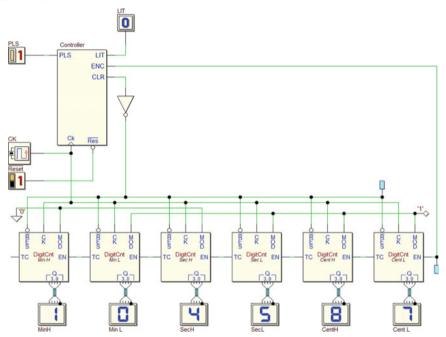

|    |       | 9.3.2    | Digital Chronometer                             | 510 |

|    | 9.4   | Solution | ns                                              | 514 |

|    |       | 9.4.1    | Synchronous Serial Communication System (8-bit) | 514 |

|    |       | 9.4.2    | Digital Chronometer                             | 515 |

| Аp | pendi | x A: The | e Powers of 2                                   | 519 |

| Аp | pendi | x B: Sta | te Diagrams                                     | 521 |

| Ap | pendi | x C: VH  | IDL Code                                        | 525 |

# Chapter 1 Boolean Algebra and Combinational Logic

1

**Abstract** This chapter introduces to the idea of digitally representing analog quantities and goes step by step through the main concepts of the Boolean algebra: variables, functions, truth tables, operations, and properties. The chapter is quite detailed and accompanied by many examples and exercises in order to provide a precise framework of the fundamentals of digital design. It includes the theorems which constitute the foundation for the application of the Boolean algebra to logic networks, with a precise focus on their application for combinational network design.

### 1.1 Analog and Discrete Variables

In every field of human knowledge, information's observation, memorization, elaboration, and communication is something everyone has to deal with. The definition of the word "information" may sound obvious, since this term is commonly used in everyday language, but for our aim we need a definition that leaves no space to any ambiguous interpretation. We hence refer to R. V. L. Hartley (1888–1970), one of the fathers of *Information Theory*, who helps us with the following definition:

Information is a reduction of uncertainty.

From this sentence, it is clear that information is associated with "before" and "after," in relation to an event having a probability to happen; thanks to this probability, an observer reduces his uncertainty related to the event itself. From this definition, it can be easily derived that information can be conveyed through the employment of physical quantities variables, changing in time or space. For example, we can refer to information transmitted by a computer screen through images, defined as variations of luminosity and color in time and space, or the information transmitted by an earphone, through a sound, defined as variations of air pressure over time.

To the aim of studying information processing, we will not refer directly to a physical quantity variable, but rather to its numeric representation, indicated with "G," and its variation over time, indicated with "T."

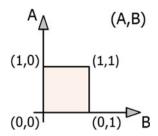

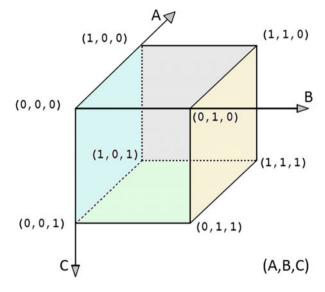

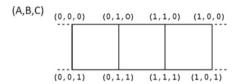

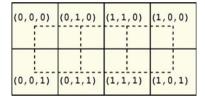

This approach allows us to divide the representation into two families: if G can vary continuously between a value and another one, assuming all the infinite intermediate

values, we are employing an "analog" representation. If, instead, *G* can assume only a limited number of values, we are employing a "discrete" (or "digital") representation, becoming "binary" (or "Boolean") if the numbering system uses only two symbols.

Sometimes, the distinction between a physical quantity variable and its numeric representation may create confusion, but we are interested only in the latter. Light, for example, may be described both through a discrete representation (*photons*) and a continuous one (*electromagnetic waves*), but identifying the "true" representation, if it exists, is beyond our scope: we gladly leave this objective to philosophers. For an engineer, what matters is using the most appropriate tool to solve the problem under analysis.

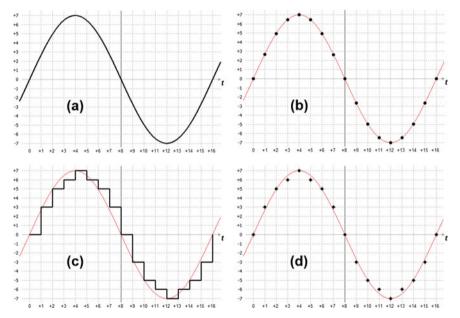

In the picture, four possible representations obtained using discrete or continuous values for G and T are provided [red lines are given for reference]:

- (a) continuous quantity variable changing over time;

- (b) continuous quantity variable sampled over time;

- (c) quantity variable quantized in amplitude and continuous over time;

- (d) quantity variable quantized in amplitude and sampled over time.

In the analog case, the main tool at our disposal is math, involving real numbers and functions defined over them: i.e., algebra and infinitesimal calculus. The analog representation is effective at dealing with natural physical quantities variables at the macroscopic level.

This does not mean that natural quantities' variables are analog, but only that in this case the analog representation is the most suitable and effective. In fact, if we go deeper toward the microscopic level, matter reveals its discrete nature (atoms

and particles) and the analog representation is not necessarily the most convenient. Generally, a device able to convert continuous quantities variables into digital ones, and vice versa, is necessary. These devices are called *Analog to Digital Converters* (ADC) and *Digital to Analog Converters* (DAC) respectively, but they are beyond the scope of this book.

The digital case may be faced with discrete math, generally more complex than real numbers math. If we limit to the case of *G* assuming only two values, i.e., the binary case, we can refer to the *Boolean algebra* that takes its name from its creator, the Irish logician and mathematician George Boole (1815–1864). *Boolean algebra* will be sufficient for our scope, that is, putting the basis of the combinational logic and digital systems.

Binary variables are usually indicated with  $\{0,1\}$  or also with other symbols, like  $\{-1,+1\}$ ,  $\{L,H\}$  (Low and High) or  $\{T,F\}$  (True or False), depending on the context.

In the digital field, we will make use of both the representation over continuous time, called "asynchronous," and the one over discrete time, called "synchronous." A logic network is called synchronous if its parts operate simultaneously, according to a common synchronization signal; it is instead defined as asynchronous if its parts operate in an autonomous mode among each other.

The binary (digital) representation possesses advantages and disadvantages with respect to the analog one:

- an analog value is a pure mathematical abstraction, since it requires infinite precision to be expressed.

- a discrete value (binary) is easily storable, since it requires a finite number (two) of the physical variable values to be memorized.

- the management and processing of binary variables are less sensitive to a possible damaging of the signals that occur during its processing and transmission. In fact, if the damage is not large enough to alter the distinction between the two signal levels (high/low), there is no damage in the information carried by signals.

- the precision of the system can be easily controlled by choosing the number of bits that code the information.

- devices processing digital information, namely digital systems, are simpler to design, though the practical realization requires a higher number of circuital components.

### 1.2 Boolean Variables

Let *X* be a certain discreet variable. We will call *Boolean variable* any discreet variable that can assume only two values. These values are denoted as follows:

$$X = 0$$

false  $X = 1$  true

In the following, the values 0, 1 will be used.

### 1.3 Boolean Functions

If we have the Boolean variables  $X_1, X_2, ..., X_n$ , the following:

$$f(X_1, X_2, \ldots, X_n)$$

is called a Boolean function, and it can assume only the values 0 and 1. This function associates a Boolean value to every element in its domain.

The domain of a function of n-variables is composed of all the  $2^n$  combinations of their values. Therefore, domain's elements are countable. Two functions are equivalent if they assume the same value for any combination of their variables' values.

### 1.4 Truth Tables

The Principle of Perfect Induction (that is, carrying out all the calculations) makes it possible to prove the value of f for all the  $2^n$  points of the domain. The function is represented in the truth table.

Let's assume a three-variable function  $X_1$ ,  $X_2$ ,  $X_3$ . We can construct a table with all the values assumed by f:

| es |

|----|

|    |

| ed |

|    |

|    |

|    |

|    |

|    |

**Observation**: To write the  $2^3 = 8$  elements of the domain, we begin at the farthest right column  $(X_3)$ , from the top and alternate between one 0 and one 1. In the next column, we alternate between two 0s and two 1s, while in the column after that, four 0s and four 1s and so on, doubling the number of 0s and 1s with each new column.

### **Examples:**

Derive the **truth tables** from the *verbal definitions*:

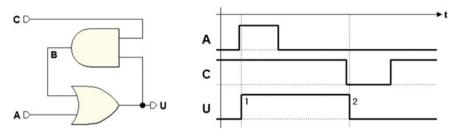

1. *U* is true if *C* is true or if *B* and *A* are both true.

1.4 Truth Tables 5

2. Z is true if the number of ones in the inputs M, G, D is equal to two.

|    |   |   | $\boldsymbol{A}$ | U |  | M | G | D | Z |

|----|---|---|------------------|---|--|---|---|---|---|

|    | 0 | 0 | 0                | 0 |  | 0 | 0 | 0 | 0 |

| 1. | 0 | 0 | 1                | 0 |  | 0 | 0 | 1 | 0 |

|    | 0 | 1 | 0                | 0 |  | 0 | 1 | 0 | 0 |

|    | 0 | 1 | 1                | 1 |  | 0 | 1 | 1 | 1 |

|    | 1 | 0 | 0                | 1 |  | 1 | 0 | 0 | 0 |

|    | 1 | 0 | 1                | 1 |  | 1 | 0 | 1 | 1 |

|    | 1 | 1 | 0                | 1 |  | 1 | 1 | 0 | 1 |

|    | 1 | 1 | 1                | 1 |  | 1 | 1 | 1 | 0 |

### 1.5 Definition of Boolean Algebra

Boolean algebra provides the necessary tools to calculate and interpret information presented in binary form. Boolean algebra is an *algebraic system* (a set of elements to which a set of operations is associated), defined by:

- The set of values  $\{0,1\}$ ;

- The operations OR, AND, and NOT;

- The equivalence operator "=", along with the properties reflexive, symmetric, and transitive.

The three operations are defined as follows:

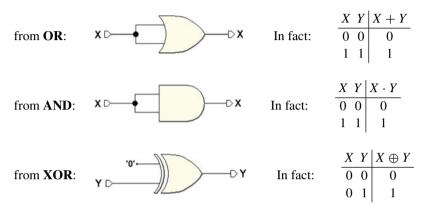

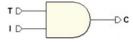

| Operation:               | OR                                                                                                              | AND                                                                                                                 | NOT                                                                        |

|--------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| •                        | (logical sum)                                                                                                   | (logical product)                                                                                                   | (negation)                                                                 |

| Algebraic symbols:       | $X + Y$ $X \lor Y$ $X \cup Y$ $X \text{ or } Y$                                                                 | $X \cdot Y = XY$ $X \wedge Y$ $X \cap Y$ $X \text{ and } Y$                                                         | $\overline{X}$ ! $X$ - $X$ not( $X$ )                                      |

| Truth table:             | $\begin{array}{c cccc} X & Y & X + Y \\ \hline 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 1 \\ \end{array}$ | $\begin{array}{c cccc} X & Y & X \cdot Y \\ \hline 0 & 0 & 0 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 1 \\ \end{array}$ | $\begin{array}{c c} X & \overline{X} \\ \hline 0 & 1 \\ 1 & 0 \end{array}$ |

| Circuit diagram symbols: | X D F                                                                                                           | Y D                                                                                                                 | F C C C C C C C C C C C C C C C C C C C                                    |

### 1.6 The Fundamental Properties of Boolean Algebra

### Conventions

- $X, Y, Z, X_1, X_2, X_3, ..., X_n$ , are considered Boolean variables.

- The parentheses establish the calculation priorities as in regular algebra.

- AND is prioritized over OR (e.g., X + YZ = X + (YZ)).

This is also analogous to regular algebra. All the properties can be demonstrated through Perfect Induction, that is, by verifying the validity of each combination of values assumed by the variables that make up the expression.

(dual:)

### **Duality Principle**

If a given expression is valid, its dual expression is also valid. The dual expression is obtained by switching the OR with the AND and the 0 constants with the 1 constants from the original expression. For example:

$$(dual:) X + 1 = 1$$

$$X \cdot 0 = 0$$

$$X + 0 = X$$

$X \cdot 1 = X$

### **Idempotent Law**

$$(dual:) X + X = X$$

$$X \cdot X = X$$

### **Commutative Law**

$$(\text{dual:}) \quad \begin{array}{l} X + Y = Y + X \\ X \cdot Y = Y \cdot X \end{array}$$

### Associative Law

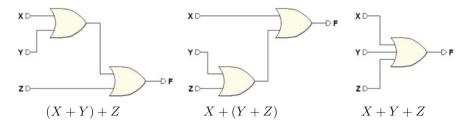

$$(X+Y)+Z=X+(Y+Z)=X+Y+Z$$

(dual:)

$$(X\cdot Y)\cdot Z=X\cdot (Y\cdot Z)=X\cdot Y\cdot Z.$$

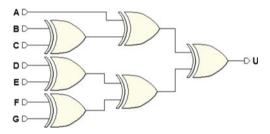

The associative law makes it possible to extend fundamental operations to more than two variables. The circuit symbols for the first expression are:

As there is no distinction between the first and second circuits, it makes sense to generally define an OR of three or more inputs. The same holds true for the AND, so it is really the property of Associativity that allows us to make sense of OR and AND gates with more than two inputs.

We can redefine the OR and AND operations with n inputs:

- An OR with *n* inputs gives a 0 as output only if all the *n* inputs are 0, otherwise it gives a 1 as output.

- An AND with *n* inputs gives a 1 as output only if all the *n* inputs are 1, otherwise it gives a 0 as output.

### **Distributivity**

Factoring law

$$(X + Y) \cdot (X + Z) = X + (Y \cdot Z)$$

Distributive law (dual:)  $(X \cdot Y) + (X \cdot Z) = X \cdot (Y + Z)$

Proof of the factoring law:

$$(X + Y) \cdot (X + Z) = X \cdot X + X \cdot Z + X \cdot Y + Y \cdot Z =$$

$$= X + X \cdot Z + X \cdot Y + Y \cdot Z$$

$$= X \cdot (1 + Y) + X \cdot Z + Y \cdot Z$$

$$= X + X \cdot Z + Y \cdot Z$$

$$= X \cdot (1 + Z) + Y \cdot Z$$

$$= X + (Y \cdot Z)$$

It would also be possible to demonstrate this law through Perfect Induction (i.e., verifying all the possible combinations for X, Y, Z):

| X Y Z | $Y \cdot Z$ | $X + Y \cdot Z$ | X + Y | X + Z | (X+Y)(X+Z) |

|-------|-------------|-----------------|-------|-------|------------|

| 0 0 0 | 0           | 0               | 0     | 0     | 0          |

| 0 0 1 | 0           | 0               | 0     | 1     | 0          |

| 0 1 0 | 0           | 0               | 1     | 0     | 0          |

| 0 1 1 | 1           | 1               | 1     | 1     | 1          |

| 1 0 0 | 0           | 1               | 1     | 1     | 1          |

| 1 0 1 | 0           | 1               | 1     | 1     | 1          |

| 1 1 0 | 0           | 1               | 1     | 1     | 1          |

| 1 1 1 | 1           | 1               | 1     | 1     | 1          |

It is clear that columns  $X + Y \cdot Z$  and (X + Y)(X + Z) are equal.

### Complementation

$$X + \overline{X} = 1$$

(dual:)  $X \cdot \overline{X} = 0$

### Absorption

First form:

$$X + X \cdot Y = X$$

(dual:)  $X \cdot (X + Y) = X$

Second form:

$$X + (\overline{X} \cdot Y) = X + Y$$

(dual:)

$$X \cdot (\overline{X} + Y) = X \cdot Y$$

Proof:

$$\begin{array}{lll} X+X\cdot Y &= X\cdot (1+Y)=X\cdot 1=X\\ X\cdot (X+Y)=X\cdot X+X\cdot Y=X+X\cdot Y=X\\ X+\overline{X}\cdot Y &= X+X\cdot Y+\overline{X}\cdot Y=X+Y(X+\overline{X})=X+Y\\ X\cdot (\overline{X}+Y)=X\cdot \overline{X}+X\cdot Y=X\cdot Y \end{array}$$

### Logic Adjacency

$$\begin{array}{ccc} Y\,X+Y\,\overline{X}=Y\\ \text{(dual:)} & (Y+X)\cdot(Y+\overline{X})=Y \end{array}$$

Proof:

$$YX + Y\overline{X} = Y \cdot (X + \overline{X}) = Y \cdot 1 = Y$$

$$(Y + X) \cdot (Y + \overline{X}) = Y + (X \cdot \overline{X}) = Y + 0 = Y$$

### Consensus

$$X \cdot Y + Y \cdot Z + Z \cdot \overline{X} = X \cdot Y + Z \cdot \overline{X}$$

(dual:)

$$(X + Y)(Y + Z)(Z + \overline{X}) = (X + Y)(Z + \overline{X})$$

Proof:

$$\begin{split} X \cdot Y + Y \cdot Z + Z \cdot \overline{X} &= \\ &= X \cdot Y + Y \cdot (X + \overline{X}) \cdot Z + Z \cdot \overline{X} = \\ &= (X \cdot Y + X \cdot Y \cdot Z) + (Z \cdot \overline{X} \cdot Y + Z \cdot \overline{X}) = \\ &= X \cdot Y + Z \cdot \overline{X} \\ (X + Y)(Y + Z)(Z + \overline{X}) &= \\ &= (X + Y)[(X + Y + Z)(\overline{X} + Y + Z)](Z + \overline{X}) = \\ &= [(X + Y)(X + Y + Z)][(Z + \overline{X} + Y)(Z + \overline{X})] = \\ &= (X + Y)(Z + \overline{X}) \end{split}$$

### Involution

Also known as Double Complement law:  $\overline{\overline{X}} = X$ .

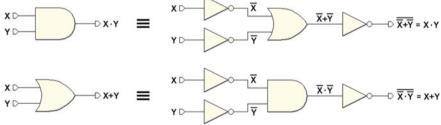

### **Duality or De Morgan's Theorem**

A logical product of two variables can be substituted by the negation of their logical sum. Dual: a logical sum of two variables can be substituted by the negation of their logical product:

$$X \cdot Y = \overline{\overline{X} + \overline{Y}}$$

(dual:)

$$X + Y = \overline{\overline{X} \cdot \overline{Y}}$$

This theorem is important: it allows us to obtain an AND through an OR gate and vice versa. The theorem tells us that either one of the two functions is superfluous according to the definition of Boolean algebra.

### Generalized De Morgan's Theorem

The theorem applies to any number of variables:

$$\begin{array}{rcl} X_1 \cdot X_2 \cdot \ldots \cdot X_n & = & \overline{\overline{X_1} + \overline{X_2} + \ldots + \overline{X_n}} \\ \text{(dual :)} & X_1 + X_2 + \ldots + X_n & = & \overline{\overline{X_1} \cdot \overline{X_2} \cdot \ldots \cdot \overline{X_n}}. \end{array}$$

### 1.7 Other Operations

In this paragraph, we define other operations in Boolean algebra: NAND, NOR, and EXOR.

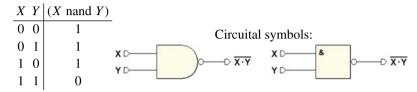

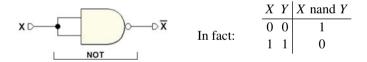

### **NAND**

The NAND operation is equivalent to an AND whose output is negated:

$$X$$

nand  $Y = \overline{(X \cdot Y)}$

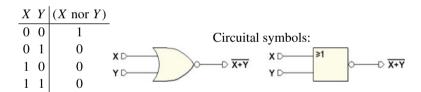

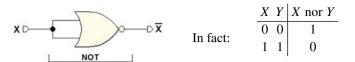

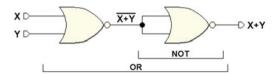

### NOR

The NOR operation is equivalent to an OR whose output is negated:

$$X \text{ nor } Y = \overline{(X + Y)}$$

NAND and NOR are commutative but not associative.

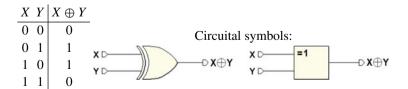

### **XOR** (Exclusive OR)

The XOR operation is said "anticoincidence" (it provides 1 when the inputs are different):

$$X \oplus Y = X \text{ xor } Y = X \overline{Y} + \overline{X} Y$$

The XOR is *commutative* and *associative*. If we negate its output, we obtain the "coincidence" function (equivalence of inputs):

$$\overline{X \oplus Y} = XY + \overline{X}\overline{Y}$$

### Generalized XOR

Is a multiple inputs XOR, written thus:

$$X_1 \oplus X_2 \oplus \ldots \oplus X_n = \begin{cases} 1 \text{ if there is an odd number of inputs} = 1 \\ 0 \text{ if there is an even number of inputs} = 1 \end{cases}$$

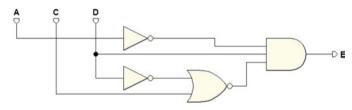

They are made with the typical structure of the XOR tree:

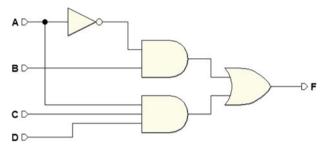

### 1.8 Functionally Complete Operation Sets

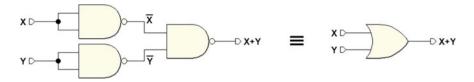

We have seen that Boolean algebra is based on a set of two elements {0, 1} and a set of operations: OR, AND, NOT. Also, De Morgan's Theorem shows that one of the two AND or OR operations can be considered superfluous and the sets of {OR, NOT} or {AND, NOT} are a sufficient basis to construct all of Boolean algebra. Let's broaden the subject by discussing other sets of operations that allows to construct Boolean algebra (named, for this reason, *Functionally Complete Operation Sets*):

- 1. {AND, OR, NOT}

- 2. {NOR}

- 3. {NAND}

- 4. {OR, NOT}

- 5. {AND, NOT}

- 6. {EXOR, AND}

- 6. {EXOR, OR}

**Note**: in practice, only {NOR} and {NAND} sets are used.

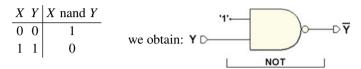

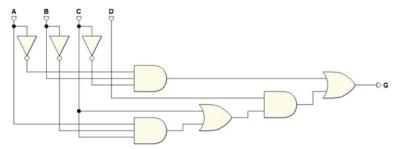

### {NOR} Set

We can obtain OR and NOT from NOR gates. If we connect a NOR as in the figure below, we obtain a NOT. Given that the *X* and *Y* inputs are connected together, we obtain the following from the NOR table:

However, we obtain the OR gate by negating the NOR output with a NOT:

To obtain the AND, we apply De Morgan:  $X \cdot Y = \overline{\overline{X} + \overline{Y}}$ . We have:

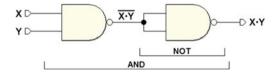

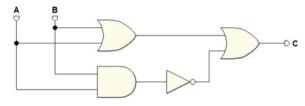

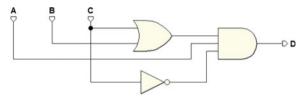

### {NAND} Set

Similar to the above, the NOT is obtained as follows, taking into account the two lines of the NAND table where the two *X* and *Y* inputs are equal:

Therefore, to obtain the AND, it is sufficient to connect the NAND to a NOT made with a NAND.

Finally, by De Morgan, we obtain the OR:

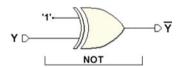

**Take note**: there is another way to obtain the NOT by the NAND. By connecting one of the inputs to the constant X = 1:

Similarly, if we posit X = 0 for the NOR we get:

### {OR, NOT} Set

The AND is obtained by De Morgan's Theorem.

### {AND, NOT} Set

The OR is obtained by De Morgan's Theorem.

### {XOR, AND} Set

The NOT is obtained by the XOR as follows:

From the XOR truth table, we get:

| X Y | $X \oplus Y$ |                    |   |   |              |

|-----|--------------|--------------------|---|---|--------------|

| 0 0 | 0            |                    | X | Y | $X \oplus Y$ |

| 0 1 | 1            | positing $X = 1$ : | 1 | 0 | 1            |

| 1 0 | 1            |                    | 1 | 1 | 0            |

| 1 1 | 0            |                    |   |   |              |

**Note**: If we change the constant X = 1 in 0, we get the identity. Therefore, we obtain an inverting/identity function, "programmable" by the input X.

### {XOR, OR} Set

The NOT is obtained through the XOR and the AND by using De Morgan's Theorem.

### **Identity**

Identity can be obtained in the following ways:

### 1.9 Shannon's Expansion Theorem

### **First Form**

A Boolean function can be broken down this way:

$$f(X_1, X_2, X_3, \dots, X_n) = \overline{X_1} \cdot f(0, X_2, X_3, \dots, X_n) + X_1 \cdot f(1, X_2, X_3, \dots, X_n)$$

The first of the two terms obtained is equivalent to the starting function but only when  $X_1 = 0$ , so it is conditioned by  $\overline{X_1}$ . Likewise, the second term, which applies to  $X_1 = 1$ , is conditioned by  $X_1$ .

Now that we have seen the process, we can extract all the variables of the function:

$$f(X_1, X_2, X_3, ..., X_n) = \overline{X_1} \cdot \overline{X_2} \cdot f(0, 0, X_3, ..., X_n) + \overline{X_1} \cdot \underline{X_2} \cdot f(0, 1, X_3, ..., X_n) + X_1 \cdot \overline{X_2} \cdot f(1, 0, X_3, ..., X_n) + X_1 \cdot X_2 \cdot f(1, 1, X_3, ..., X_n) = ...$$

In the end, every f(0, 1, ...)-type entry will turn out to be a (0 or 1) constant. From an n-variable function, we obtain  $2^n$  product terms in OR, where each term consists of all the direct and negated variables.

As an example, let's break down a f(C, B, A) into three variables:

$$f(C, B, A) = \overline{C} \, \overline{B} \, \overline{A} \cdot f(0, 0, 0) + \\ \overline{C} \, \overline{B} \, A \cdot f(0, 0, 1) + \\ \overline{C} \, B \, \overline{A} \cdot f(0, 1, 0) + \\ \overline{C} \, B \, \overline{A} \cdot f(0, 1, 1) + \\ C \, \overline{B} \, \overline{A} \cdot f(1, 0, 0) + \\ C \, \overline{B} \, A \cdot f(1, 0, 1) + \\ C \, B \, \overline{A} \cdot f(1, 1, 0) + \\ C \, B \, A \cdot f(1, 1, 1)$$

The expanded form of the function is called *sum of products*, or *first canonical form*, or *AND–OR form*.

### **Example**

We want to derive the analytical expression from a Boolean function f(C, B, A) defined through the truth table using the first form of the theorem.

Beginning by the definition, we substitute all the f(...)-type constants with the real value of the function, taken directly from the truth table. We observe that in the logical sum, the terms with 0 in AND can be omitted since they are always 0. We then simplify the remaining terms corresponding to the lines with output 1 and eliminate the product for the constant. The remaining expression is what we're looking for. It analytically expresses the behavior of the function in the *first canonical form*.

### Second Form

The second form allows us to break down a function f into a product of sums:

$$f(X_1, X_2, X_3, \dots, X_n) = (X_1 + f(0, X_2, X_3, \dots, X_n)) \cdot (\overline{X_1} + f(1, X_2, X_3, \dots, X_n))$$

The first sum term is equivalent to the starting function after substituting  $X_1 = 0$  and applies if  $X_1 = 0$  (otherwise the whole term is 1). The second sum term is equivalent

to the starting function after substituting  $X_1 = 1$  and applies if  $X_1 = 1$  (otherwise the whole term is 1). In other words, for a certain value of  $X_1$ , one of the two terms is always 1, while the other assumes the value of the function.

If we go through the break-down procedure until we exhaust all the f argument variables, we obtain  $2^n$  terms in AND. Each term is composed of the logical sum of all the direct or negated variables and the value of the function for that specific combination:

$$f(X_1, X_2, X_3, ..., X_n) = (X_1 + X_2 + f(0, 0, X_3, ..., X_n)) \cdot (X_1 + \overline{X_2} + f(0, 1, X_3, ..., X_n)) \cdot (\overline{X_1} + X_2 + f(1, 0, X_3, ..., X_n)) \cdot (\overline{X_1} + \overline{X_2} + f(1, 1, X_3, ..., X_n)) = ...$$

Consider a three-variable function f(C, B, A); we obtain  $2^3$  OR terms in AND:

$$f(C, B, A) = (C + B + A + f(0, 0, 0)) \cdot (C + B + \overline{A} + f(0, 0, 1)) \cdot (C + \overline{B} + A + f(0, 1, 0)) \cdot (C + \overline{B} + \overline{A} + f(0, 1, 1)) \cdot (\overline{C} + B + A + f(1, 0, 0)) \cdot (\overline{C} + B + \overline{A} + f(1, 0, 1)) \cdot (\overline{C} + \overline{B} + A + f(1, 1, 0)) \cdot (\overline{C} + \overline{B} + \overline{A} + f(1, 1, 1)) \cdot (\overline{C} + \overline{B} + \overline{A} + f(1, 1, 1))$$

A function expanded this way takes on the second canonical form, or product of sums, or OR-AND form. Any Boolean function can be expressed this way. For a function with n-variables, we obtain  $2^n$  factors to multiply.

### **Example**

Through the second form of Shannon's Expansion Theorem, we derive the analytical expression of a Boolean function f(C, B, A), given the truth table that describes it.

We have applied the definition of the second form of the theorem by substituting all the f(...)-type constants with the values of the truth table. Given that the constant term 1 in a logical sum absorbs the other variables and that adding 0 is redundant, the function's final expression is:

$$f = (C + \overline{B} + A) \cdot (C + \overline{B} + \overline{A}) \cdot (\overline{C} + B + A)$$

The expression expresses how the function behaves in the second canonical form.

## 1.10 Level of Boolean Expressions

The level is the maximum number of cascading operations made on the input variables. For example:

$$f = a + b$$

is a one-level expression  $f = ab + c$  is a two-level expression  $f = ab + cd$  is a two-level expression

**Take note**: the levels are important for technical reasons. The more levels there are, the longer the delays; we will focus mainly on syntheses of two-level networks. When the number of levels has to be computed, we suppose all the input variables and their complemented forms to be available. Thus, the expression  $f = \overline{a}b + \overline{c}d$  is a two-level Boolean expression.

### 1.11 Literals

Literals are the number of input variables that make up a Boolean expression (not to be confused with the number of variables).

For example: if f(a, b) is a logical function with two binary variables a and b:

$$f = a + b$$

has 2 literals  $f = ab + \overline{a}b$  has 4 literals.

### 1.12 Minterms

If an AND term in a Boolean expression contains all the direct or negated variables in the entire expression, it is called a *fundamental product*, or *minterm*. For example:

$$f(X_1, X_2, X_3) = X_1 \cdot X_2 \cdot \overline{X_3}$$

is a minterm.

An *n*-variable function has  $2^n$  minterms since every variable in the function must be part of a minterm, in its direct or negated form. Note that among all the possible combinations of variables, there is only one for which a certain minterm equals 1 (e.g.,  $X_1 \cdot X_2 \cdot \overline{X_3} = 1$  if and only if  $X_1 = 1$ ,  $X_2 = 1$ ,  $X_3 = 0$ ).

### 1.13 Maxterms

If an OR term in a Boolean expression contains all the direct or negated variables in the entire expression, it is called a *fundamental sum*, or *maxterm*. As above, if there are n-variables, there are  $2^n$  maxterms. For example:

$$f(X_1, X_2, X_3) = X_1 + \overline{X_2} + X_3$$

is a maxterm.

Remember that there is only one combination of variables for which a certain maxterm equals zero (e.g.,  $X_1 + \overline{X_2} + X_3 = 0$  if and only if  $X_1 = 0$ ,  $X_2 = 1$ ,  $X_3 = 0$ ).

# 1.14 Implicants

Given the Boolean expressions f and g, g is an implicant of f: g implies f ( $g \Rightarrow f$ ) or f covers g ( $f \supset g$ ) if f always = 1 when g = 1.

In this example:

$$f(X, Y, Z) = XY + Z$$

we have  $XY \Rightarrow f$

$Z \Rightarrow f$

Every time Z and/or XY equal 1, f also equals 1. XY and Z are therefore implicants of f. X does not imply f: in fact if X equals 1 f does not necessarily equal 1.

# 1.15 Prime Implicants

g is a *prime* implicant of f if:

•

$$q \Rightarrow f(f \supset q)$$

;

• g is not covered by another implicant with fewer literals.

In other words, an implicant is prime if it equals 1 when no other implicant equals 1. An implicant, which *is not* prime, can be removed from the expression since it is superfluous. In the example:

$$f = XY + X + Z$$

X and Z are prime implicants while XY is a non-prime implicant of f. In fact, to have XY = 1 it is necessary that X = 1, but if X = 1 then f = 1 anyway, since X already implies  $f(X \supset XY)$ .

### 1.16 Combinational Networks

A *combinational network* is defined as a logical circuit whose output depends only on the combination of its inputs. In Chap. 5, we will discuss *sequential networks* whose output does not only depend on the values of the inputs in that time but also on the "inputs history." In other words, we will see that these networks have memory capacity.

A combinational network can be described in terms of a Boolean function. Note some examples of combinational networks.

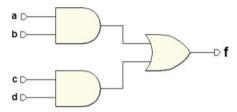

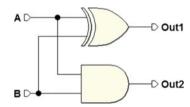

## 1.16.1 Example: Logical Network Analysis

We want to analyze the following circuit, obtaining its truth table:

It is composed of two known gates, so we can complete the truth table directly:

| $\boldsymbol{A}$ | В | Out1 | Out2 |

|------------------|---|------|------|

| 0                | 0 | 0    | 0    |

| 0                | 1 | 1    | 0    |

| 1                | 0 | 1    | 0    |

| 1                | 1 | 0    | 1    |

We will find this circuit again in Chap. 2, being an arithmetic circuit.