# Introduction to Logic Circuits & Logic Design with VHDL

## Introduction to Logic Circuits & Logic Design with VHDL

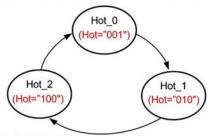

2<sup>ND</sup> EDITION

**Brock J. LaMeres**

Brock J. LaMeres

Department of Electrical & Computer Engineering

Montana State University

Bozeman, MT, USA

ISBN 978-3-030-12488-5 ISBN 978-3-030-12489-2 (eBook) https://doi.org/10.1007/978-3-030-12489-2

Library of Congress Control Number: 2019932161

© Springer Nature Switzerland AG 2017, 2019

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors, and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Cover credit: ID 98722794 © Vladimir Timofeev | Dreamstime.com

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

### **Preface**

The overall goal of this book is to fill a void that has appeared in the instruction of digital circuits over the past decade due to the rapid abstraction of system design. Up until the mid-1980s, digital circuits were designed using classical techniques. Classical techniques relied heavily on manual design practices for the synthesis, minimization, and interfacing of digital systems. Corresponding to this design style, academic textbooks were developed that taught classical digital design techniques. Around 1990, large-scale digital systems began being designed using hardware description languages (HDL) and automated synthesis tools. Broad-scale adoption of this modern design approach spread through the industry during this decade. Around 2000, hardware description languages and the modern digital design approach began to be taught in universities, mainly at the senior and graduate level. There were a variety of reasons that the modern digital design approach did not penetrate the lower levels of academia during this time. First, the design and simulation tools were difficult to use and overwhelmed freshman and sophomore students. Second, the ability to implement the designs in a laboratory setting was infeasible. The modern design tools at the time were targeted at custom integrated circuits, which are cost- and time-prohibitive to implement in a university setting. Between 2000 and 2005, rapid advances in programmable logic and design tools allowed the modern digital design approach to be implemented in a university setting, even in lower-level courses. This allowed students to learn the modern design approach based on HDLs and prototype their designs in real hardware, mainly field programmable gate arrays (FPGAs). This spurred an abundance of textbooks to be authored teaching hardware description languages and higher levels of design abstraction. This trend has continued until today. While abstraction is a critical tool for engineering design, the rapid movement toward teaching only the modern digital design techniques has left a void for freshman- and sophomore-level courses in digital circuitry. Legacy textbooks that teach the classical design approach are outdated and do not contain sufficient coverage of HDLs to prepare the students for follow-on classes. Newer textbooks that teach the modern digital design approach move immediately into high-level behavioral modeling with minimal or no coverage of the underlying hardware used to implement the systems. As a result, students are not being provided the resources to understand the fundamental hardware theory that lies beneath the modern abstraction such as interfacing, gate-level implementation, and technology optimization. Students moving too rapidly into high levels of abstraction have little understanding of what is going on when they click the "compile and synthesize" button of their design tool. This leads to graduates who can model a breadth of different systems in an HDL but have no depth into how the system is implemented in hardware. This becomes problematic when an issue arises in a real design and there is no foundational knowledge for the students to fall back on in order to debug the problem.

This book addresses the lower-level foundational void by providing a comprehensive, bottoms-up coverage of digital systems. The book begins with a description of lower-level hardware including binary representations, gate-level implementation, interfacing, and simple combinational logic design. Only after a foundation has been laid in the underlying hardware theory is the VHDL language introduced. The VHDL introduction gives only the basic concepts of the language in order to model, simulate, and synthesize combinational logic. This allows the students to gain familiarity with the language and the modern design approach without getting overwhelmed by the full capability of the language. The book then covers sequential logic and finite-state machines at the component level. Once this secondary foundation has been laid, the remaining capabilities of VHDL are presented that allow sophisticated, synchronous systems to be modeled. An entire chapter is then dedicated to examples of sequential system modeling, which allows the students to learn by example. The second part of the textbook introduces the details of programmable logic, semiconductor memory, and arithmetic circuits. The book

culminates with a discussion of computer system design, which incorporates all of the knowledge gained in the previous chapters. Each component of a computer system is described with an accompanying VHDL implementation, all while continually reinforcing the underlying hardware beneath the HDL abstraction.

#### Written the Way It Is Taught

The organization of this book is designed to follow the way in which the material is actually learned. Topics are presented only once sufficient background has been provided by earlier chapters to fully understand the material. An example of this learning-oriented organization is how the VHDL language is broken into two chapters. Chapter 5 presents an introduction to VHDL and the basic constructs to model combinational logic. This is an ideal location to introduce the language because the reader has just learned about combinational logic theory in Chap. 4. This allows the student to begin gaining experience using the VHDL simulation tools on basic combinational logic circuits. The more advanced constructs of VHDL such as sequential modeling and test benches are presented in Chap. 8 only after a thorough background in sequential logic is presented in Chap. 7. Another example of this learning-oriented approach is how arithmetic circuits are not introduced until Chap. 12. While technically the arithmetic circuits in Chap. 12 are combinational logic circuits and could be presented in Chap. 4, the student does not have the necessary background in Chap. 4 to fully understand the operation of the arithmetic circuitry, so its introduction is postponed.

This incremental, just-in-time presentation of material allows the book to follow the way the material is actually taught in the classroom. This design also avoids the need for the instructor to assign sections that move back and forth through the text. This not only reduces course design effort for the instructor but allows the student to know where they are in the sequence of learning. At any point, the student should know the material in prior chapters and be moving toward understanding the material in subsequent ones.

An additional advantage of this book's organization is that it supports giving the student hands-on experience with digital circuitry for courses with an accompanying laboratory component. The flow is designed to support lab exercises that begin using discrete logic gates on a breadboard and then move into HDL-based designs implemented on off-the-shelf FPGA boards. Using this approach to a laboratory experience gives the student experience with the basic electrical operation of digital circuits, interfacing, and HDL-based designs.

#### **Learning Outcomes**

Each chapter begins with an explanation of its learning objective followed by a brief preview of the chapter topics. The specific learning outcomes are then presented for the chapter in the form of concise statements about the measurable knowledge and/or skills the student will be able to demonstrate by the end of the chapter. Each section addresses a single, specific learning outcome. This eases the process of assessment and gives specific details on student performance. There are over 1000 assessment tools in the form of exercise problems and concept check questions that are tied directly to specific learning outcomes for both formative and summative assessment.

#### Teaching by Example

With nearly 250 worked examples, concept checks for each section, 200+ supporting figures, and 1000+ assessment problems, students are provided with multiple ways to learn. Each topic is described in a clear, concise written form with accompanying figures as necessary. This is then followed by annotated worked examples that match the form of the exercise problems at the end of each chapter. Additionally, concept check questions are placed at the end of each section in the book to measure the student's general understanding of the material using a concept inventory assessment style. These features provide the student multiple ways to learn the material and build an understanding of digital circuitry.

#### **Course Design**

The book can be used in multiple ways. The first is to use the book to cover two, semester-based college courses in digital logic. The first course in this sequence is an *introduction to logic circuits* and covers Chaps. 1, 2, 3, 4, 5, 6, and 7. This introductory course, which is found in nearly all accredited electrical and computer engineering programs, gives students a basic foundation in digital hardware and interfacing. Chapters 1, 2, 3, 4, 5, 6, and 7 only cover relevant topics in digital circuits to make room for a thorough introduction to VHDL. At the end of this course, students have a solid foundation in digital circuits and are able to design and simulate VHDL models of concurrent and hierarchical systems. The second course in this sequence covers *logic design* using Chaps. 8, 9, 10, 11, 12, and 13. In this second course, students learn the advanced features of VHDL such as packages, sequential behavioral modeling, and test benches. This provides the basis for building larger digital systems such as registers, finite-state machines, and arithmetic circuits. Chapter 13 brings all of the concepts together through the design of a simple 8-bit computer system that can be simulated and implemented using many off-the-shelf FPGA boards.

This book can also be used in a more accelerated digital logic course that reaches a higher level of abstraction in a single semester. This is accomplished by skipping some chapters and moving quickly through others. In this use model, it is likely that Chap. 2 on number systems and Chap. 3 on digital circuits would be quickly referenced but not covered in detail. Chapters 4 and 7 could also be covered quickly in order to move rapidly into VHDL modeling without spending significant time looking at the underlying hardware implementation. This approach allows a higher level of abstraction to be taught but provides the student with the reference material so that they can delve in the details of the hardware implementation if interested.

All exercise and concept problems that do not involve a VHDL model are designed so that they can be implemented as a multiple-choice or numeric entry question in a standard course management system. This allows the questions to be automatically graded. For the VHDL design questions, it is expected that the students will upload their VHDL source files and screenshots of their simulation waveforms to the course management system for manual grading by the instructor or teaching assistant.

#### **Instructor Resources**

Instructors adopting this book can access a growing collection of supplementary learning resources including *YouTube* videos created by the author, a solutions manual, a laboratory manual, and VHDL test benches for all problems. Additional resources are made available as demand grows. The YouTube videos cover every section in the book and can provide supplementary learning materials for students or facilitate fully online or flipped delivery of this material. The videos are found at <a href="https://www.youtube.com/c/DigitalLogicProgramming\_LaMeres">https://www.youtube.com/c/DigitalLogicProgramming\_LaMeres</a>. The solutions manual contains a graphic-rich description of select exercise problems. A complementary lab manual has also been developed to provide additional learning activities based on both the 74HC discrete logic family and an off-the-shelf FPGA board. This manual is provided separately from the book in order to support the ever-changing technology options available for laboratory exercises.

#### What's New in the Second Edition

The most common request from adopters of the first edition of this book was more assessment problems and accompanying videos. As a result, the second edition now contains over 1000 assessment questions, and YouTube videos have been created for every section of the book. Additionally, more worked examples have been added so that every section has abundant examples of how to apply the content to designing and analyzing digital circuits.

Brock J. LaMeres Bozeman, MT, USA

#### **Acknowledgments**

Endless thanks are given to my beautiful wife and soul mate, JoAnn. Every day is a gift with you by my side.

## **Contents**

| 1: INTROI | DUCTION: ANALOG VS. DIGITAL                     |

|-----------|-------------------------------------------------|

| 1.1 DIF   | FERENCES BETWEEN ANALOG AND DIGITAL SYSTEMS     |

| 1.2 ADV   | VANTAGES OF DIGITAL SYSTEMS OVER ANALOG SYSTEMS |

| 2: NUMBE  | ER SYSTEMS                                      |

| 2.1 Pos   | SITIONAL NUMBER SYSTEMS                         |

|           | Generic Structure                               |

|           | Decimal Number System (Base 10)                 |

| 2.1.3     | Binary Number System (Base 2)                   |

| 2.1.4     | Octal Number System (Base 8)                    |

| 2.1.5     | Hexadecimal Number System (Base 16)             |

| 2.2 Bas   | SE CONVERSION                                   |

| 2.2.1     | Converting to Decimal                           |

| 2.2.2     | Converting from Decimal                         |

| 2.2.3     | Converting Between 2 <sup>n</sup> Bases         |

| 2.3 BIN   | ARY ARITHMETIC                                  |

| 2.3.1     | Addition (Carries)                              |

| 2.3.2     | Subtraction (Borrows)                           |

| 2.4 Uns   | SIGNED AND SIGNED NUMBERS                       |

| 2.4.1     | Unsigned Numbers                                |

| 2.4.2     | Signed Numbers                                  |

| 3: DIGITA | L CIRCUITRY AND INTERFACING4                    |

| 3.1 Bas   | sic Gates                                       |

|           | Describing the Operation of a Logic Circuit     |

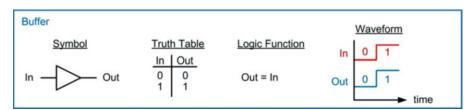

|           | The Buffer 4                                    |

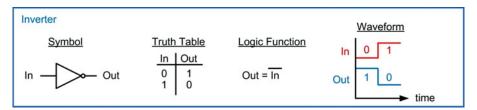

|           | The Inverter 4                                  |

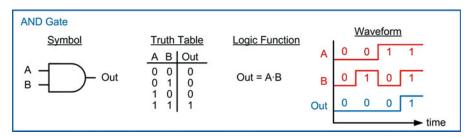

|           | The AND Gate 4                                  |

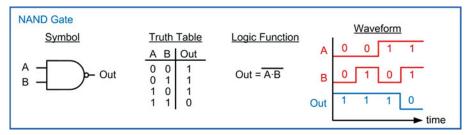

|           | The NAND Gate 4                                 |

|           | The OR Gate                                     |

|           | The NOR Gate 4                                  |

|           | The XOR Gate                                    |

|           | The XNOR Gate                                   |

|           | ITAL CIRCUIT OPERATION                          |

|           | Logic Levels                                    |

|           | Output DC Specifications                        |

|           | Input DC Specifications                         |

|           | Noise Margins                                   |

|           | Power Supplies                                  |

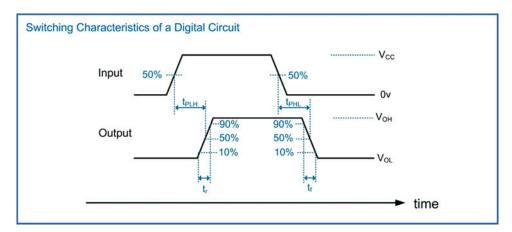

|           | Switching Characteristics                       |

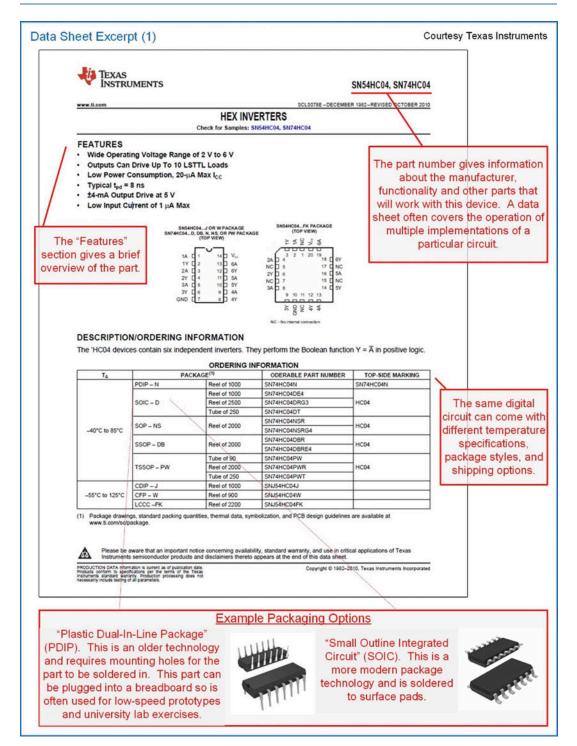

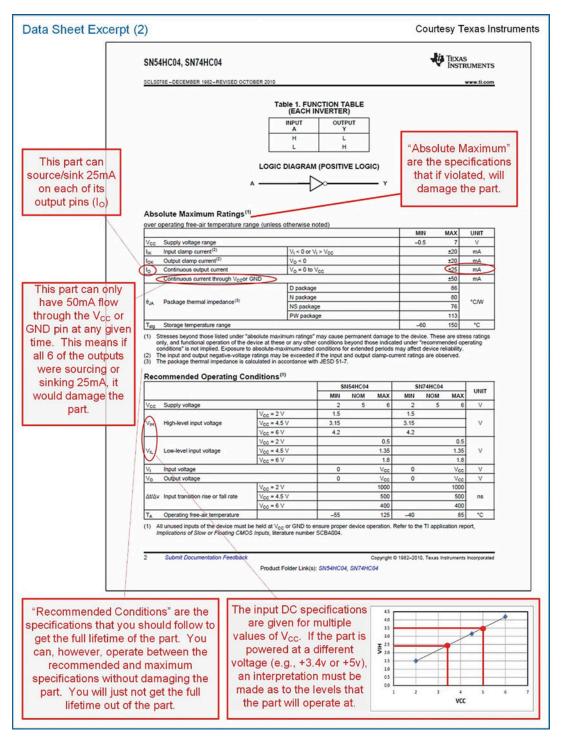

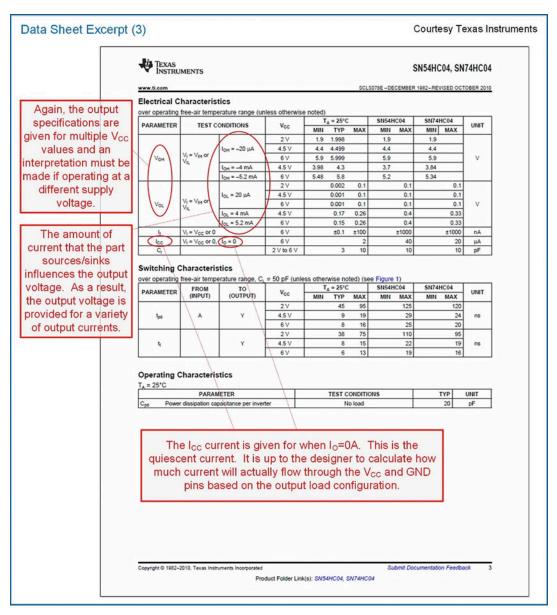

|           | Data Sheets                                     |

| 3.3 LOGIC FAMILIES                                                          | 62         |

|-----------------------------------------------------------------------------|------------|

| 3.3.1 Complementary Metal Oxide Semiconductors (CMOS)                       | 62         |

| 3.3.2 Transistor-Transistor Logic (TTL)                                     | 71         |

| 3.3.3 The 7400 Series Logic Families                                        | 73         |

| 3.4 Driving Loads                                                           | 77         |

| 3.4.1 Driving Other Gates                                                   | 77         |

| 3.4.2 Driving Resistive Loads                                               | 79         |

| 3.4.3 Driving LEDs                                                          | 81         |

| 4: COMBINATIONAL LOGIC DESIGN                                               | 93         |

| 4.1 Boolean Algebra                                                         | 93         |

| 4.1.1 Operations                                                            | 94         |

| 4.1.2 Axioms                                                                | 94         |

| 4.1.3 Theorems                                                              | 95         |

| 4.1.4 Functionally Complete Operation Sets                                  | 110        |

| 4.7.4 Functionary Complete Operation Sets  4.2 Combinational Logic Analysis | 111        |

| 4.2.1 Finding the Logic Expression from a Logic Diagram                     | 111        |

| 4.2.2 Finding the Truth Table from a Logic Diagram                          | 112        |

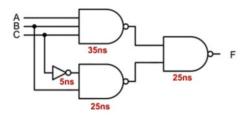

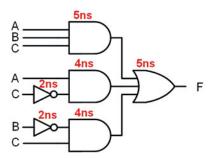

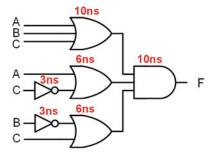

| 4.2.3 Timing Analysis of a Combinational Logic Circuit                      | 113        |

| 4.3 Combinational Logic Synthesis                                           | 115        |

| 4.3.1 Canonical Sum of Products                                             | 115        |

|                                                                             | 118        |

| 4.3.2 The Minterm List (Σ)                                                  | 119        |

| 4.3.3 Canonical Product of Sums (POS)                                       | 122        |

| 4.3.4 The Maxterm List (II)                                                 | 123        |

| 4.3.5 Minterm and Maxterm List Equivalence                                  | 125        |

| 4.4 Logic Minimization                                                      | 125        |

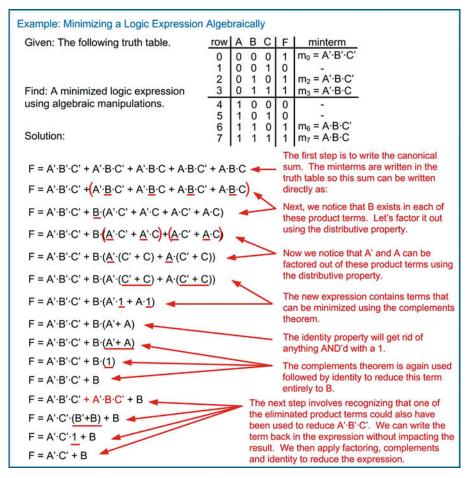

| 4.4.1 Algebraic Minimization                                                | 128        |

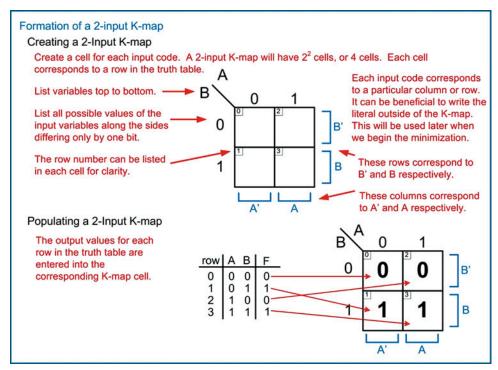

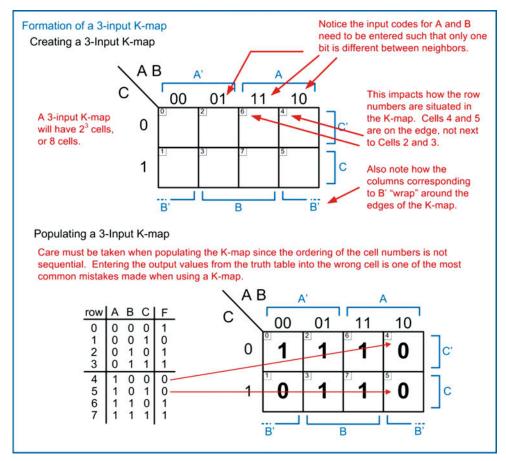

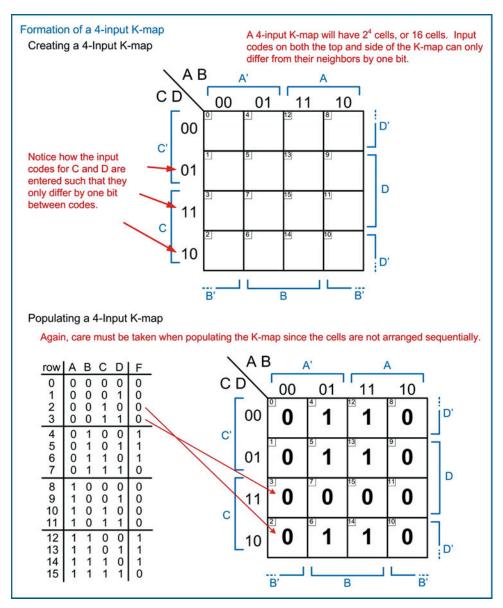

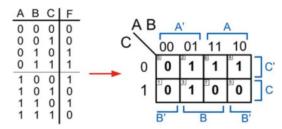

| 4.4.2 Minimization Using Karnaugh Maps                                      |            |

| 4.4.3 Don't Cares                                                           | 139<br>139 |

| 4.4.4 Using XOR Gates                                                       |            |

| 4.5 TIMING HAZARDS AND GLITCHES                                             | 142        |

| 5: VHDL (PART 1)                                                            | 155        |

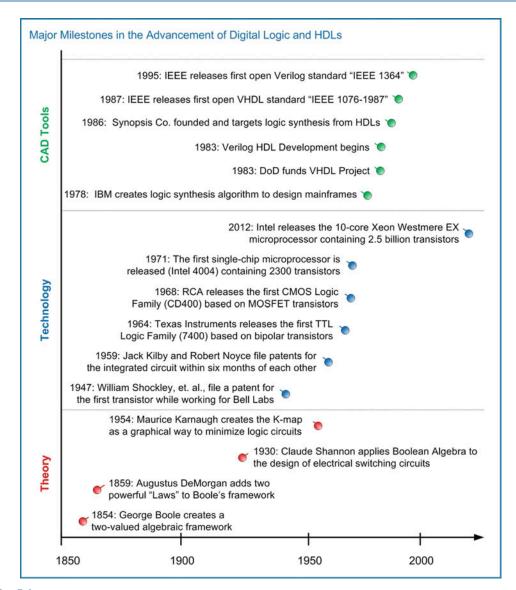

| 5.1 History of Hardware Description Languages                               | 156        |

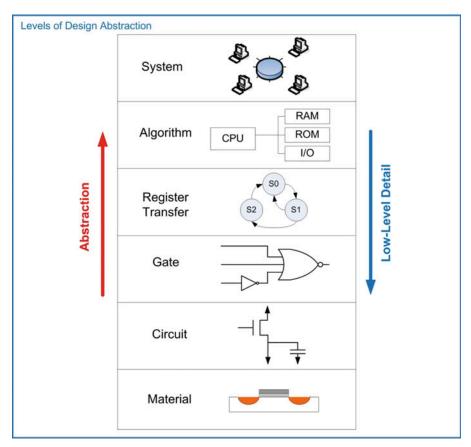

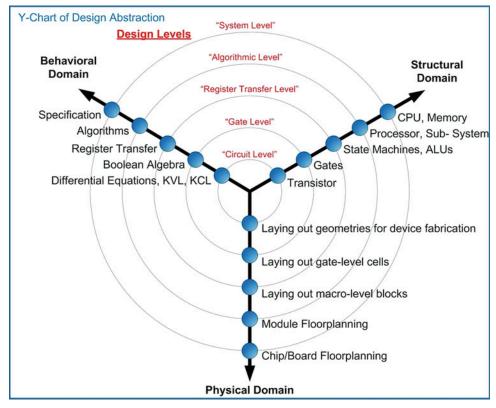

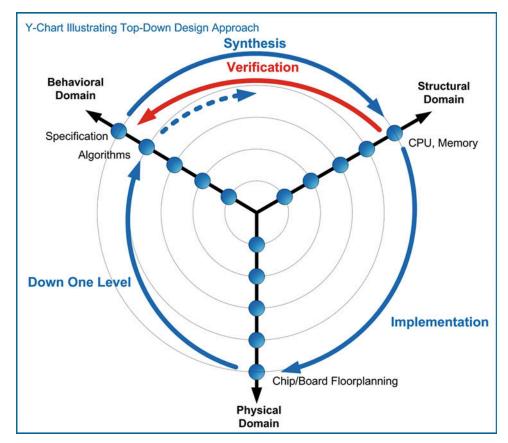

| 5.2 HDL Abstraction                                                         | 159        |

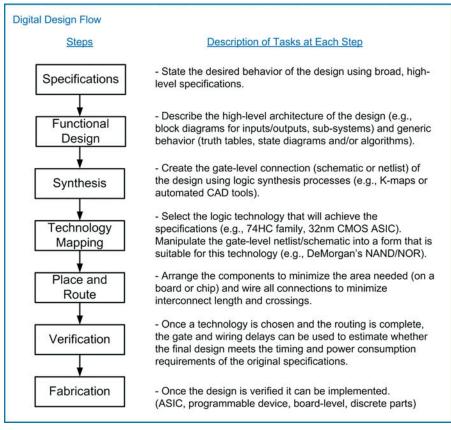

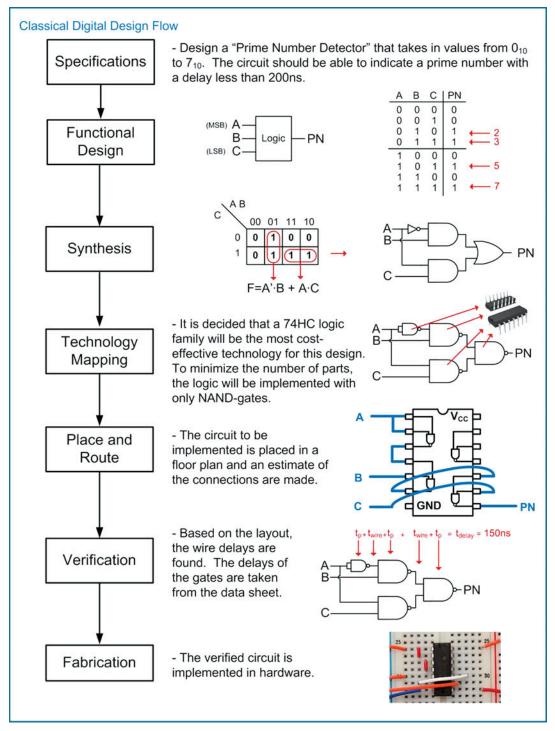

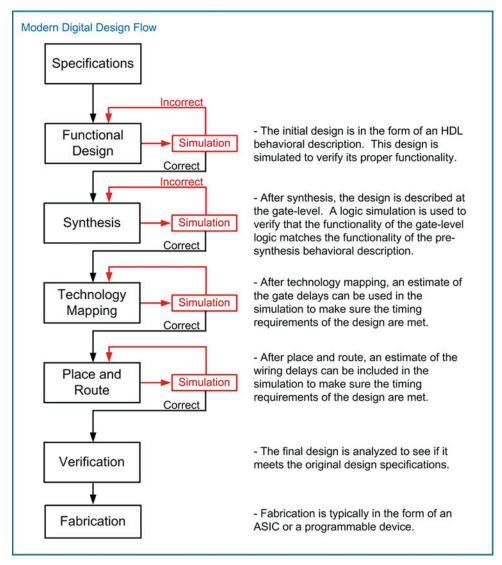

| 5.3 THE MODERN DIGITAL DESIGN FLOW                                          | 162        |

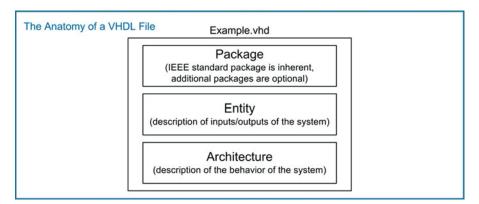

| 5.4 VHDL Constructs                                                         | 165        |

| 5.4.1 Data Types                                                            | 166        |

| 5.4.2 Libraries and Packages                                                | 168        |

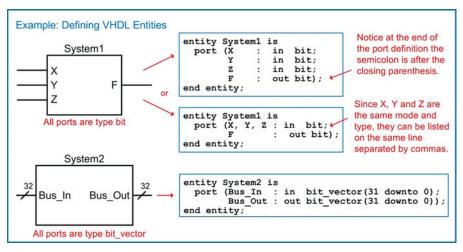

| 5.4.3 The Entity                                                            | 168        |

| 5.4.4 The Architecture                                                      | 169        |

| 5.5 Modeling Concurrent Functionality in VHDL                               | 171        |

| 5.5.1 VHDL Operators                                                        | 171        |

| 5.5.2 Concurrent Signal Assignments                                         | 174        |

| 5.5.3            | Concurrent Signal Assignments with Logical Operators       | 174        |

|------------------|------------------------------------------------------------|------------|

|                  | Conditional Signal Assignments                             | 175        |

|                  | Selected Signal Assignments                                | 177        |

|                  | Delayed Signal Assignments                                 | 178        |

|                  | JCTURAL DESIGN USING COMPONENTS                            | 181        |

|                  | Component Instantiation                                    | 181        |

|                  | RVIEW OF SIMULATION TEST BENCHES                           | 183        |

|                  | GIC                                                        | 191        |

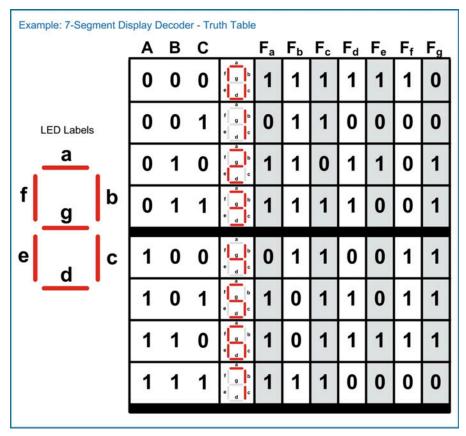

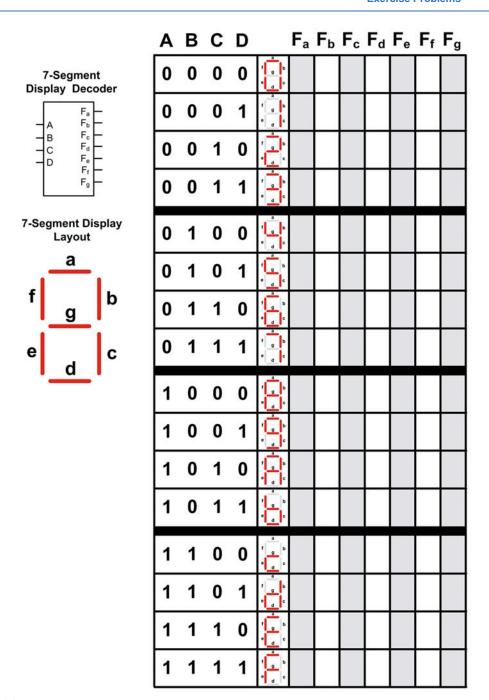

| 6.1 Dec          | ODERS                                                      | 191        |

|                  |                                                            | 191        |

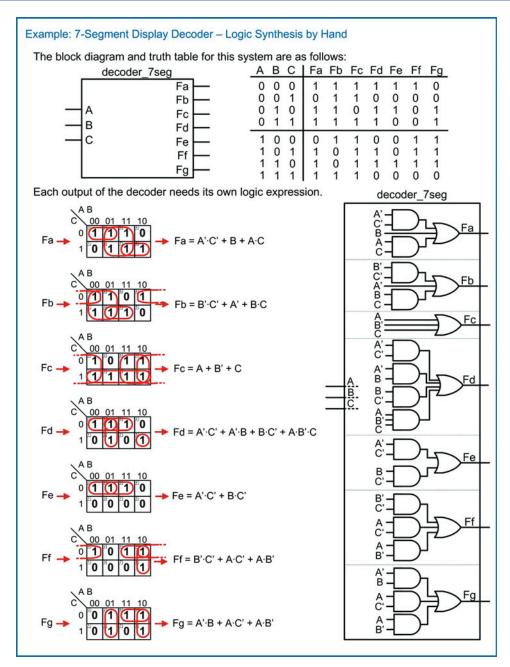

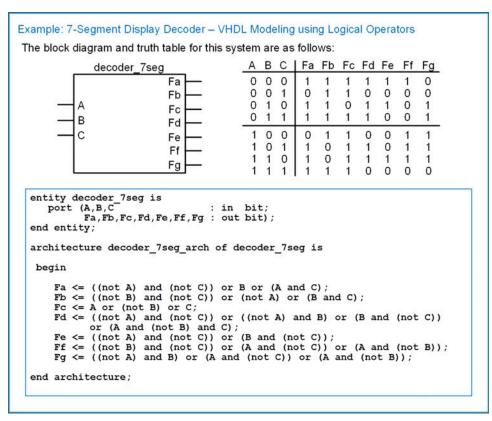

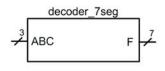

|                  | Example: One-Hot DecoderExample: 7-Segment Display Decoder | 191        |

|                  |                                                            |            |

|                  | DDERS                                                      | 199<br>199 |

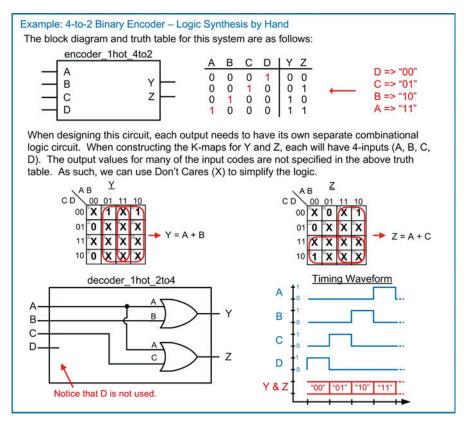

|                  | Example: One-Hot Binary Encoder                            |            |

|                  | ULTIPLEXERS                                                | 201        |

|                  |                                                            | 203        |

| 7: SEQUE         | NTIAL LOGIC DESIGN                                         | 211        |

| 7.1 <b>S</b> EQ  | JENTIAL LOGIC STORAGE DEVICES                              | 211        |

| 7.1.1            | The Cross-Coupled Inverter Pair                            | 211        |

| 7.1.2            | Metastability                                              | 212        |

| 7.1.3            | The SR Latch                                               | 214        |

| 7.1.4            | The S'R' Latch                                             | 217        |

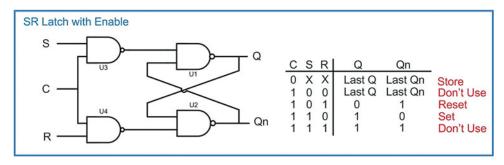

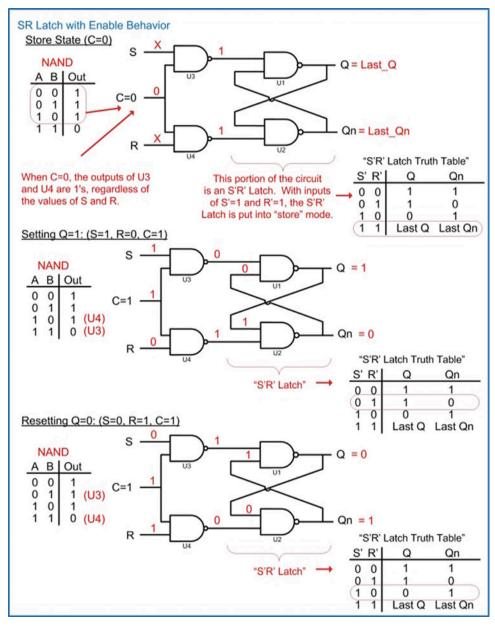

| 7.1.5            | SR Latch with Enable                                       | 220        |

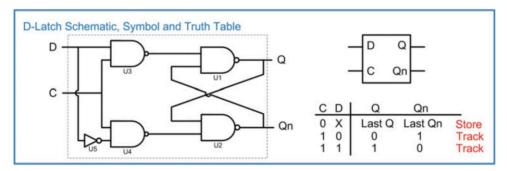

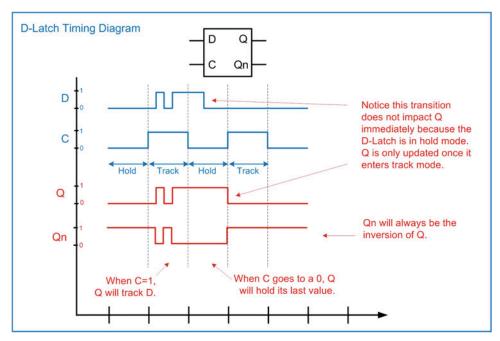

| 7.1.6            | The D-Latch                                                | 221        |

| 7.1.7            | The D-Flip-Flop                                            | 223        |

| 7.2 SEQ          | JENTIAL LOGIC TIMING CONSIDERATIONS                        | 227        |

| 7.3 <b>C</b> om  | MON CIRCUITS BASED ON SEQUENTIAL STORAGE DEVICES           | 228        |

| 7.3.1            | Toggle Flop Clock Divider                                  | 228        |

| 7.3.2            | Ripple Counter                                             | 229        |

| 7.3.3            | Switch Debouncing                                          | 230        |

| 7.3.4            | Shift Registers                                            | 234        |

| <b>7.4</b> FINIT | E STATE MACHINES                                           | 236        |

| 7.4.1            | Describing the Functionality of a FSM                      | 236        |

| 7.4.2            | Logic Synthesis for a FSM                                  | 238        |

| 7.4.3            | FSM Design Process Overview                                | 245        |

| 7.4.4            | FSM Design Examples                                        | 246        |

| <b>7.5</b> Cou   | NTERS                                                      | 253        |

| 7.5.1            | 2-Bit Binary Up Counter                                    | 253        |

| 7.5.2            | 2-Bit Binary Up/Down Counter                               | 255        |

| 7.5.3            | 2-Bit Gray Code Up Counter                                 | 256        |

| 7.5.4            | 2-Bit Gray Code Up/Down Counter                            | 258        |

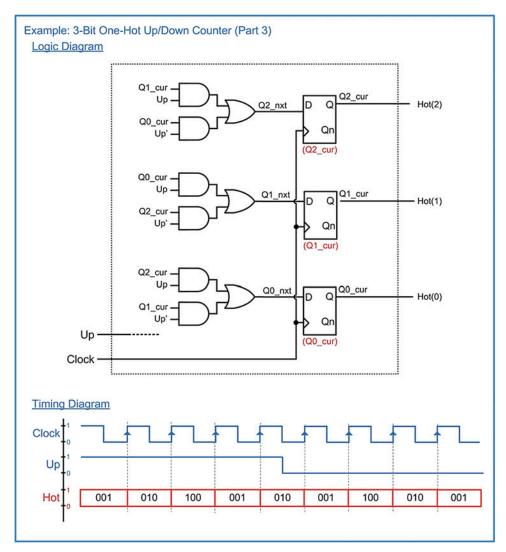

|                  | 3-Bit One-Hot Up Counter                                   | 260        |

|                  | 3-Bit One-Hot Up/Down Counter                              | 262        |

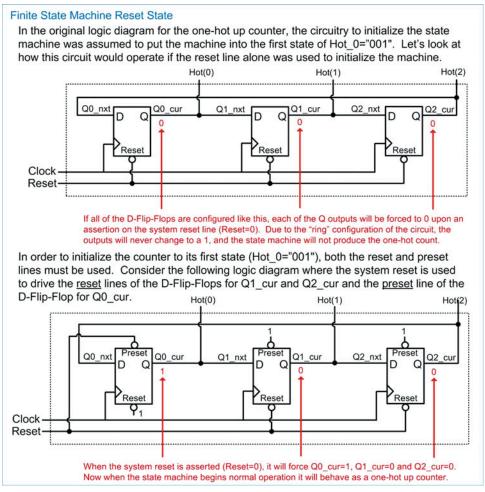

| 76 FINIT         | E STATE MACHINE'S RESET CONDITION                          | 266        |

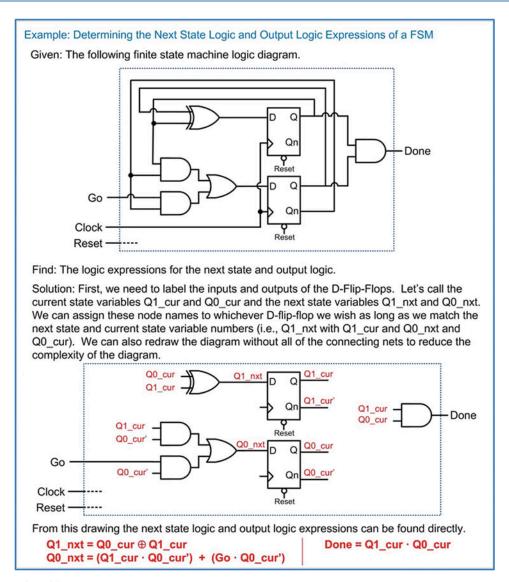

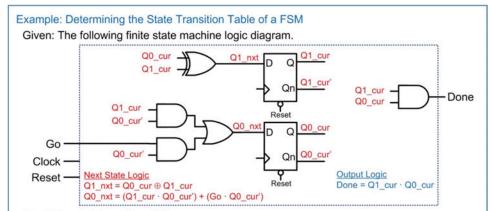

| 7.7 SEQUE   | ENTIAL LOGIC ANALYSIS                                        | 267 |

|-------------|--------------------------------------------------------------|-----|

|             | Finding the State Equations and Output Logic                 |     |

|             | Expressions of a FSM                                         | 267 |

|             | -inding the State Transition Table of a FSM                  | 268 |

|             | Finding the State Diagram of a FSM                           | 269 |

| 7.7.4 D     | Determining the Maximum Clock Frequency of a FSM             | 270 |

| 8: VHDL (PA | ART 2)                                                       | 285 |

| 8.1 THE F   | PROCESS                                                      | 285 |

|             | Sensitivity List                                             | 285 |

|             | The Wait Statement                                           | 286 |

|             | Sequential Signal Assignments                                | 287 |

|             | /ariables                                                    | 289 |

|             | ITIONAL PROGRAMMING CONSTRUCTS                               | 290 |

|             | f/Then Statements                                            | 290 |

| 8.2.2 C     | Case Statements                                              | 292 |

|             | nfinite Loops                                                | 293 |

|             | Vhile Loops                                                  | 295 |

|             | For Loops                                                    | 295 |

|             | ATTRIBUTES                                                   | 296 |

|             | Benches                                                      | 298 |

|             | Report Statement                                             | 299 |

|             | Assert Statement                                             | 300 |

|             | AGES                                                         | 302 |

|             | STD_LOGIC_1164                                               | 302 |

|             | NUMERIC_STD                                                  | 306 |

|             | NUMERIC_STD_UNSIGNED                                         | 308 |

|             | NUMERIC_BIT                                                  | 308 |

|             | NUMERIC_BIT_UNSIGNED                                         | 309 |

|             | MATH REAL                                                    | 309 |

|             | MATH COMPLEX                                                 | 311 |

|             | EXTIO and STD_LOGIC_TEXTIO                                   | 311 |

|             | egacy Packages (STD_LOGIC_ARITH/UNSIGNED/SIGNED)             | 322 |

| 9: BEHAVIC  | DRAL MODELING OF SEQUENTIAL LOGIC                            | 329 |

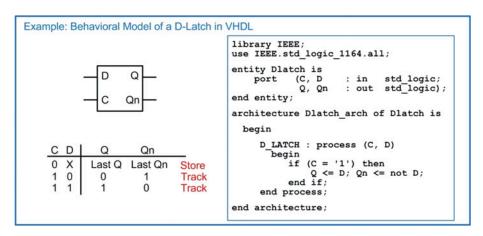

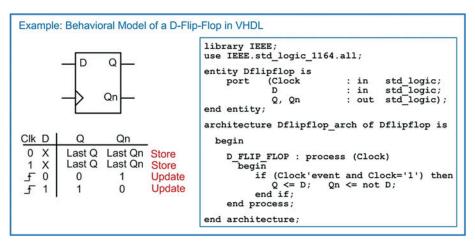

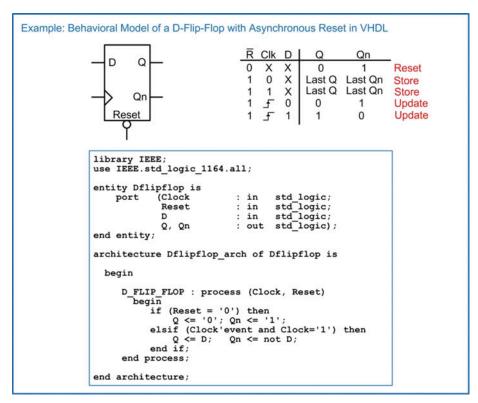

| 9.1 Mode    | LING SEQUENTIAL STORAGE DEVICES IN VHDL                      | 329 |

| 9.1.1 E     | O-Latch                                                      | 329 |

| 9.1.2 E     | D-Flip-Flop                                                  | 330 |

|             | D-Flip-Flop with Asynchronous Reset                          | 330 |

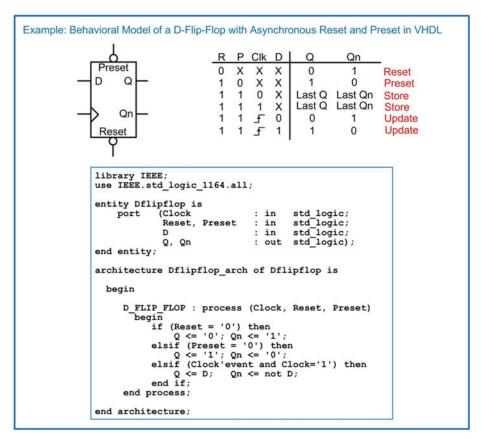

|             | D-Flip-Flop with Asynchronous Reset and Preset               | 331 |

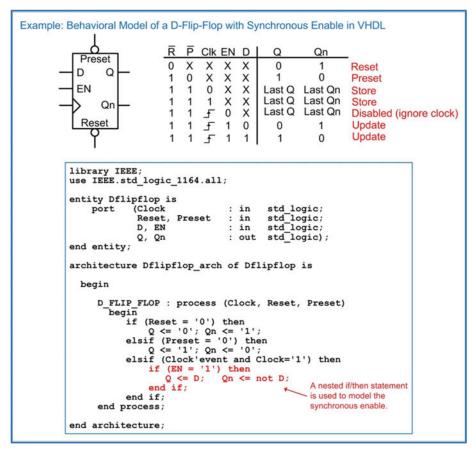

|             | D-Flip-Flop with Synchronous Enable                          | 332 |

|             | LING FINITE STATE MACHINES IN VHDL                           | 334 |

|             | Modeling the States with User-Defined, Enumerated Data Types | 335 |

|             | The State Memory Process                                     | 335 |

|             | The Next State Logic Process                                 | 336 |

|             | The Output Logic Process                                     | 336 |

|             | Explicitly Defining State Codes with Subtypes                | 338 |

|             | , J                                                          |     |

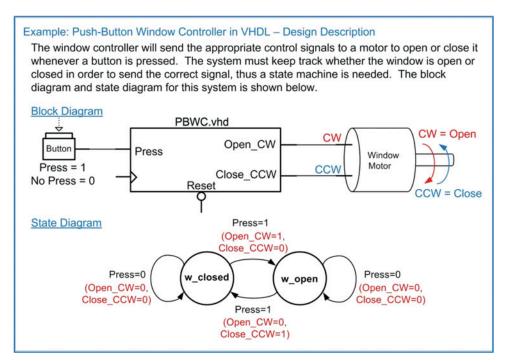

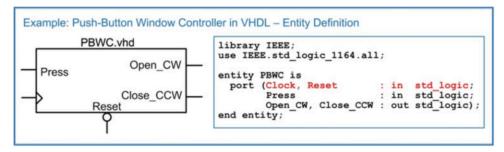

| 9.3 FSM Design Examples in VHDL                                     | 339 |

|---------------------------------------------------------------------|-----|

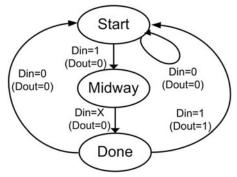

| 9.3.1 Serial Bit Sequence Detector in VHDL                          | 339 |

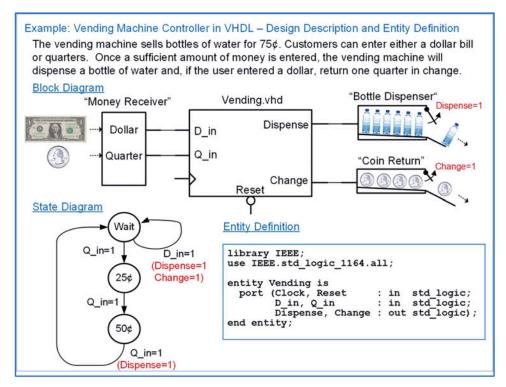

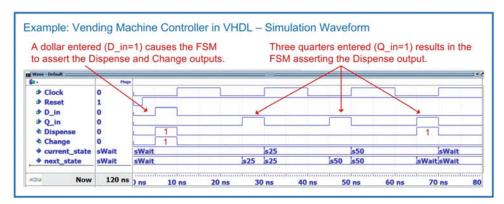

| 9.3.2 Vending Machine Controller in VHDL                            | 341 |

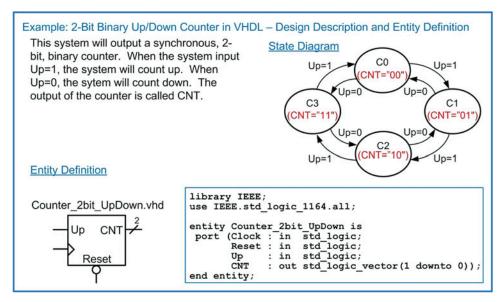

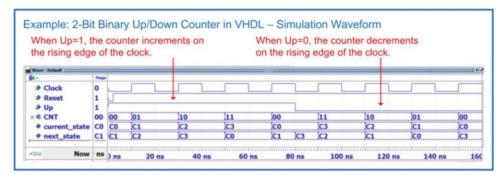

| 9.3.3 2-Bit, Binary Up/Down Counter in VHDL                         | 343 |

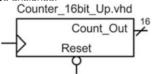

| 9.4 Modeling Counters in VHDL                                       | 345 |

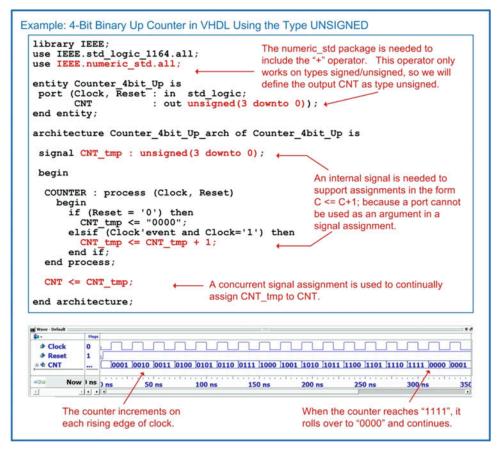

| 9.4.1 Counters in VHDL Using the Type UNSIGNED                      | 345 |

| 9.4.2 Counters in VHDL Using the Type INTEGER                       | 346 |

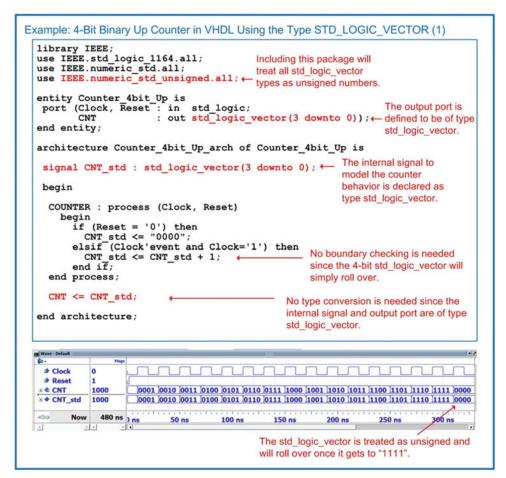

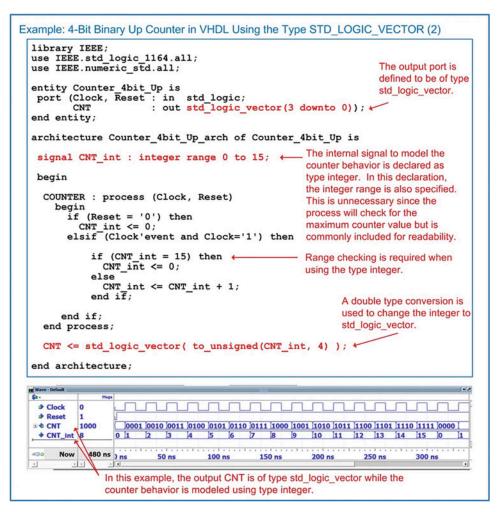

| 9.4.3 Counters in VHDL Using the Type STD_LOGIC_VECTOR              | 347 |

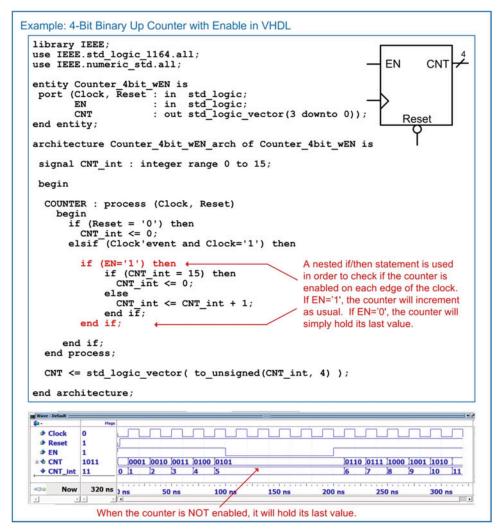

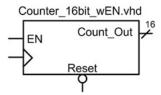

| 9.4.4 Counters with Enables in VHDL                                 | 349 |

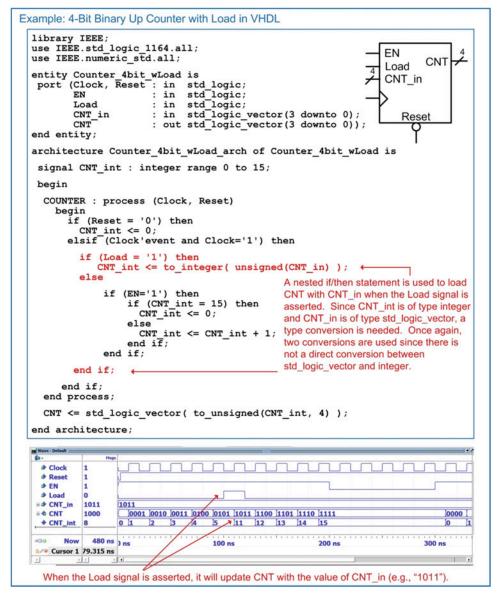

| 9.4.5 Counters with Loads                                           | 350 |

| 9.5 RTL Modeling                                                    | 352 |

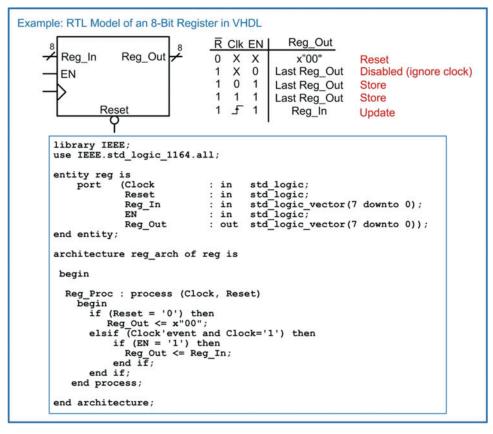

| 9.5.1 Modeling Registers in VHDL                                    | 352 |

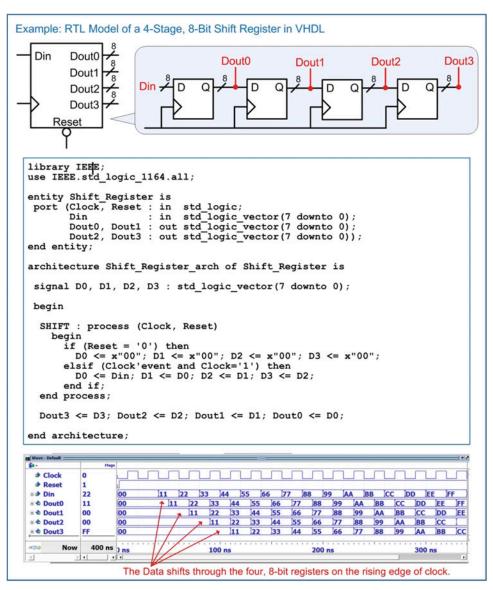

| 9.5.2 Shift Registers in VHDL                                       | 353 |

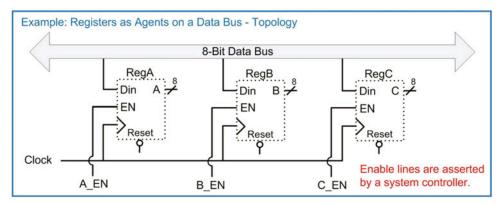

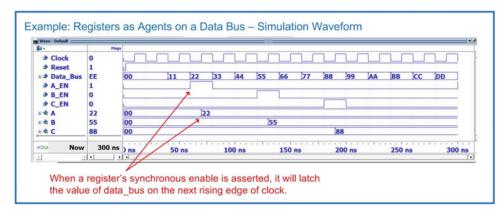

| 9.5.3 Registers as Agents on a Data Bus                             | 354 |

|                                                                     |     |

| 10: MEMORY                                                          | 361 |

| 10.1 Memory Architecture and Terminology                            | 361 |

| 10.1.1 Memory Map Model                                             | 361 |

| 10.1.2 Volatile Versus Non-volatile Memory                          | 362 |

| 10.1.3 Read-Only Versus Read/Write Memory                           | 362 |

| 10.1.4 Random Access Versus Sequential Access                       | 362 |

| 10.2 Non-volatile Memory Technology                                 | 363 |

| 10.2.1 ROM Architecture                                             | 363 |

| 10.2.2 Mask Read-Only Memory (MROM)                                 | 366 |

| 10.2.3 Programmable Read-Only Memory (PROM)                         | 367 |

| 10.2.4 Erasable Programmable Read-Only Memory (EPROM)               | 368 |

| 10.2.5 Electrically Erasable Programmable Read-Only Memory (EEPROM) | 370 |

| 10.2.6 FLASH Memory                                                 | 371 |

| 10.3 Volatile Memory Technology                                     | 371 |

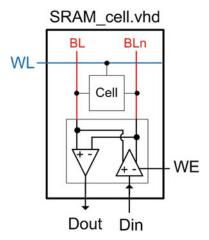

| 10.3.1 Static Random Access Memory (SRAM)                           | 372 |

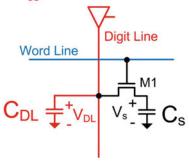

| 10.3.2 Dynamic Random Access Memory (DRAM)                          | 375 |

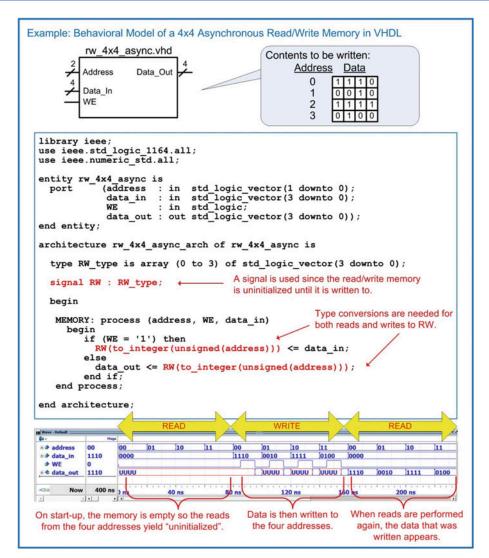

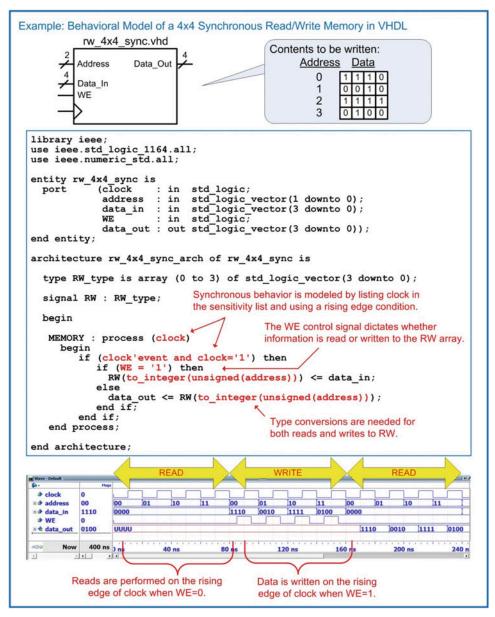

| 10.4 Modeling Memory with VHDL                                      | 382 |

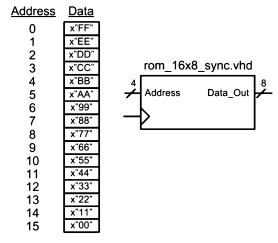

| 10.4.1 Read-Only Memory in VHDL                                     | 382 |

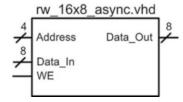

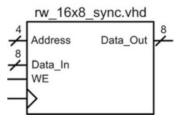

| 10.4.2 Read/Write Memory in VHDL                                    | 384 |

| •                                                                   | 202 |

| 11: PROGRAMMABLE LOGIC                                              | 393 |

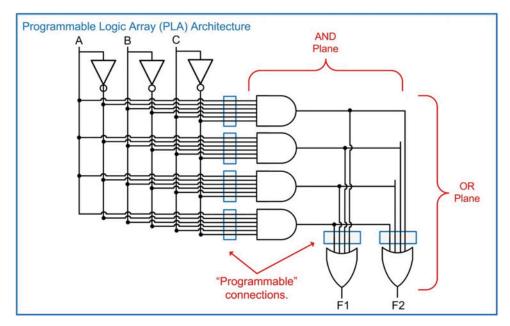

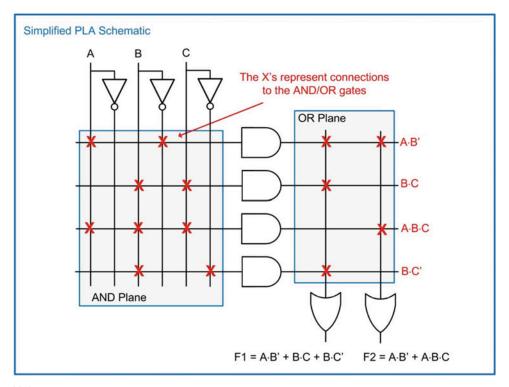

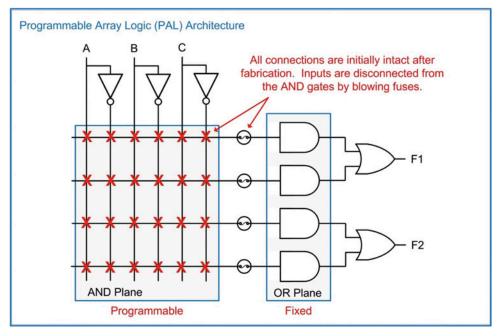

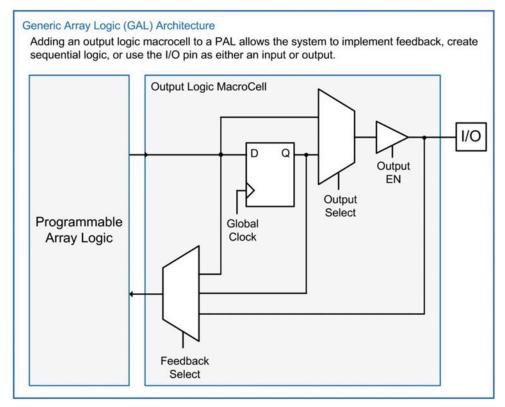

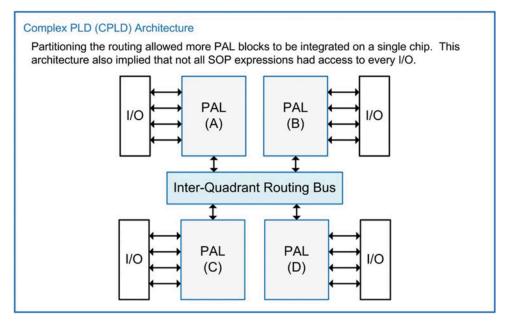

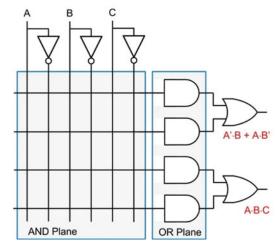

| 11.1 Programmable Arrays                                            | 393 |

| 11.1.1 Programmable Logic Array (PLA)                               | 393 |

| 11.1.2 Programmable Array Logic (PAL)                               | 394 |

| 11.1.3 Generic Array Logic (GAL)                                    | 395 |

| 11.1.4 Hard Array Logic (HAL)                                       | 396 |

| 11.1.5 Complex Programmable Logic Devices (CPLDs)                   | 396 |

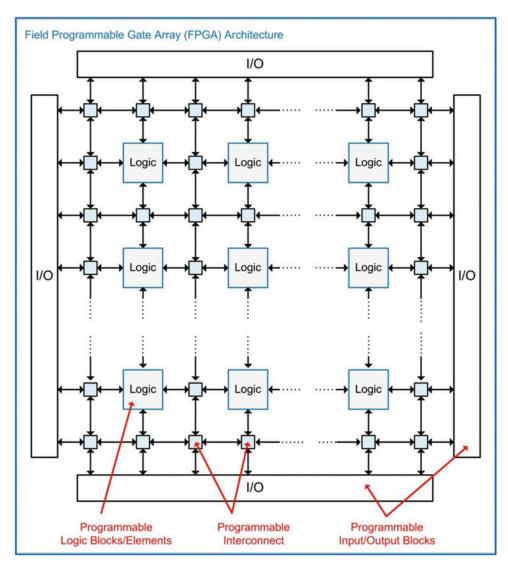

| 11.2 FIELD-PROGRAMMABLE GATE ARRAYS (FPGAs)                         | 397 |

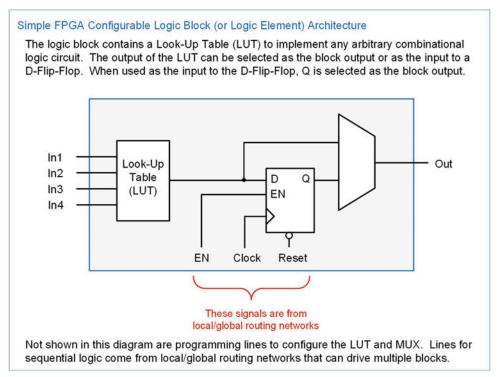

| 11.2.1 Configurable Logic Block (or Logic Element)                  | 398 |

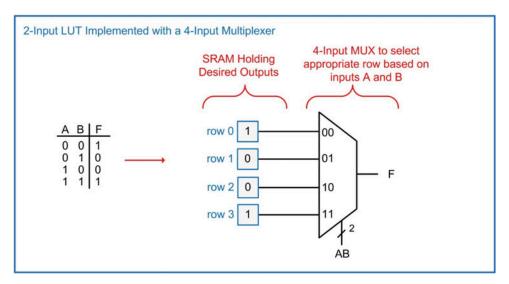

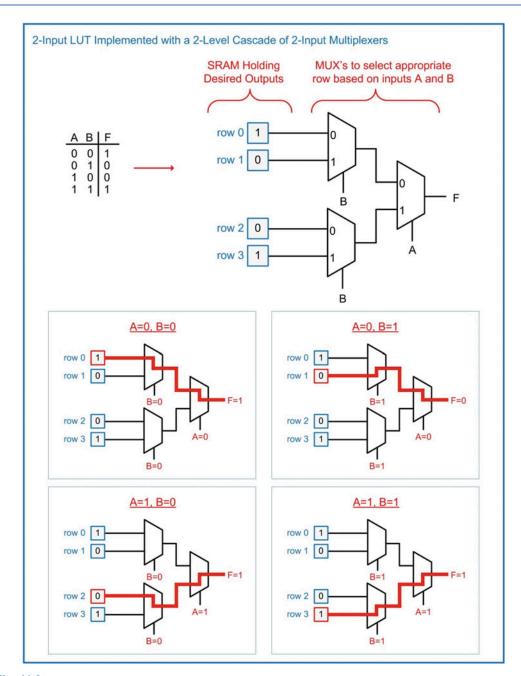

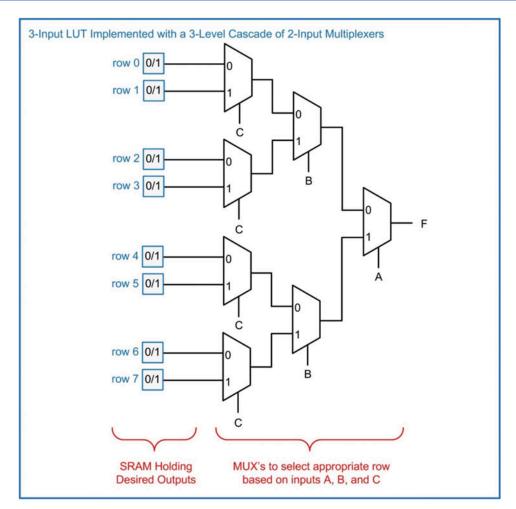

| 11.2.2 Look-Up Tables (LUTs)                                        | 399 |

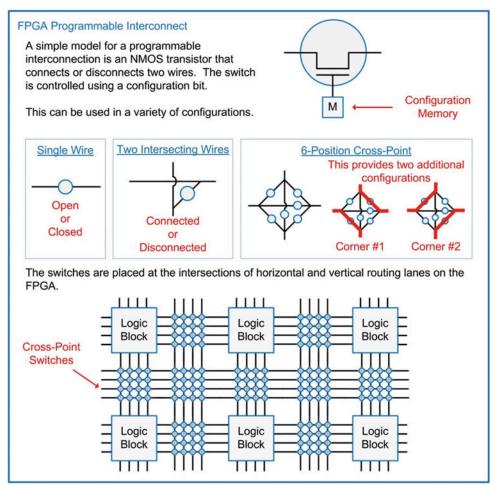

| 11.2.3 Programmable Interconnect Points (PIPs)                      | 402 |

|                                                                     |     |

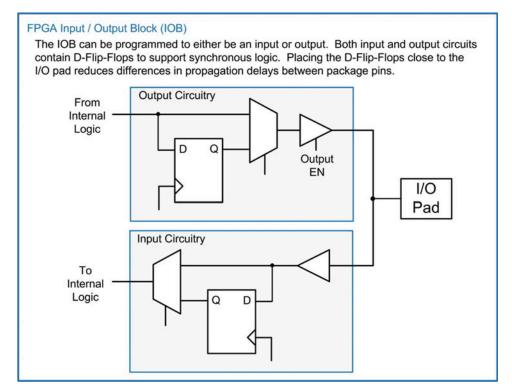

| 11.2.4 Input/Output Blocks (IOBs)                       | 403 |

|---------------------------------------------------------|-----|

| 11.2.5 Configuration Memory                             | 404 |

| 12: ARITHMETIC CIRCUITS                                 | 407 |

| 12.1 Addition                                           | 407 |

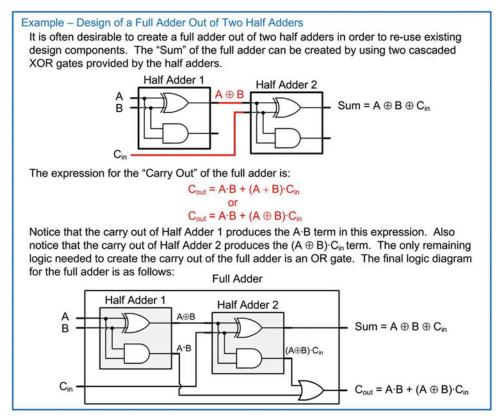

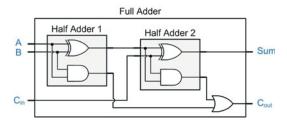

| 12.1.1 Half Adders                                      | 407 |

| 12.1.2 Full Adders                                      | 408 |

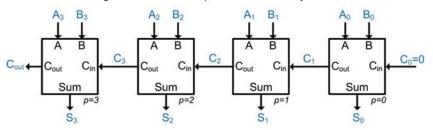

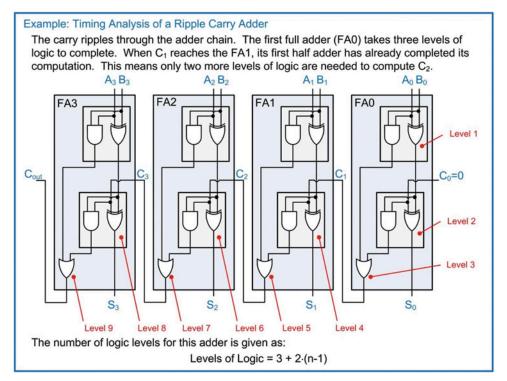

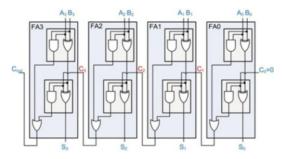

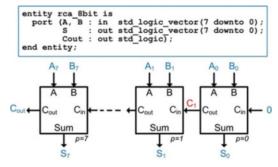

| 12.1.3 Ripple Carry Adder (RCA)                         | 410 |

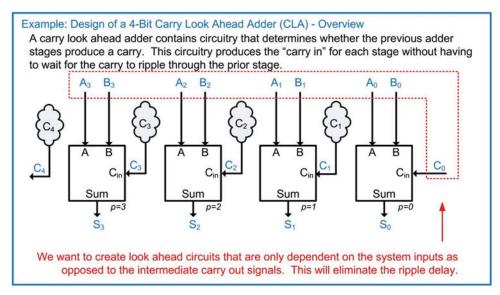

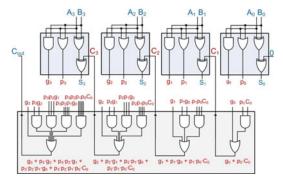

| 12.1.4 Carry Look Ahead Adder (CLA)                     | 412 |

| 12.1.5 Adders in VHDL                                   | 415 |

| 12.2 Subtraction                                        | 421 |

| 12.3 Multiplication                                     | 424 |

| 12.3.1 Unsigned Multiplication                          | 424 |

| 12.3.2 A Simple Circuit to Multiply by Powers of Two    | 427 |

| 12.3.3 Signed Multiplication                            | 428 |

| 12.4 DIVISION                                           | 430 |

| 12.4.1 Unsigned Division                                | 430 |

| 12.4.2 A Simple Circuit to Divide by Powers of Two      | 433 |

| 12.4.3 Signed Division                                  | 434 |

| 13: COMPUTER SYSTEM DESIGN                              | 439 |

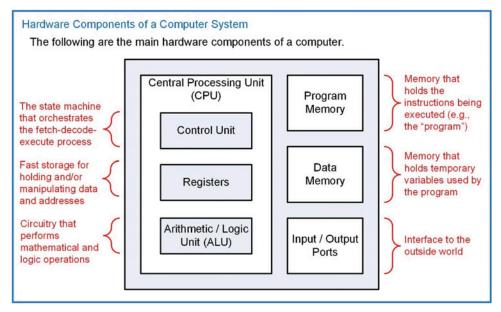

| 13.1 Computer Hardware                                  | 439 |

| 13.1.1 Program Memory                                   | 440 |

| 13.1.2 Data Memory                                      | 440 |

| 13.1.3 Input/Output Ports                               | 440 |

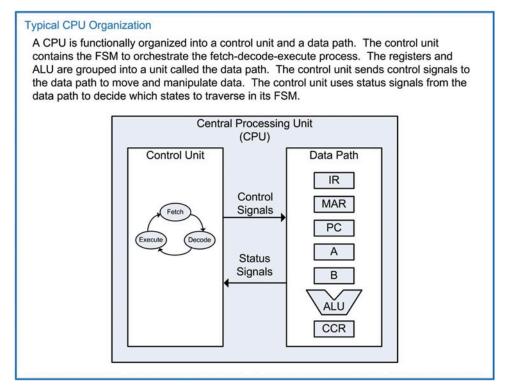

| 13.1.4 Central Processing Unit                          | 441 |

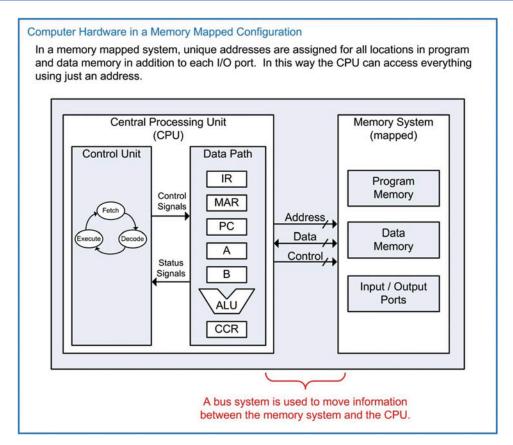

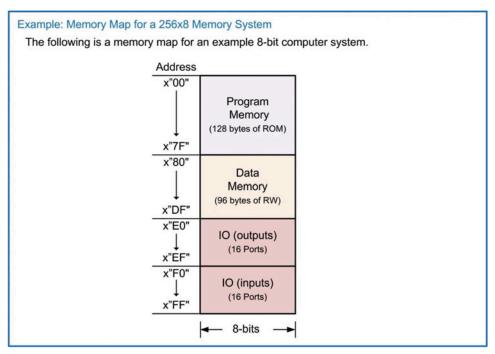

| 13.1.5 A Memory Mapped System                           | 442 |

| 13.2 Computer Software                                  | 444 |

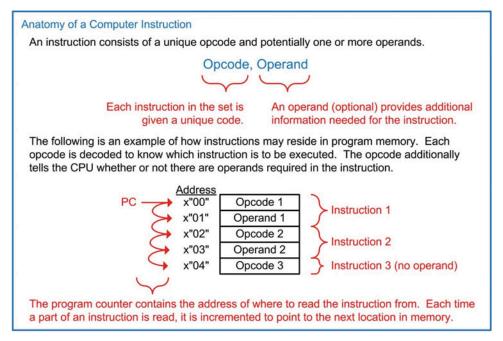

| 13.2.1 Opcodes and Operands                             | 445 |

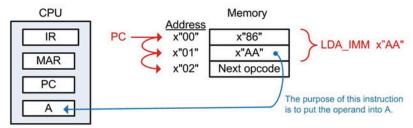

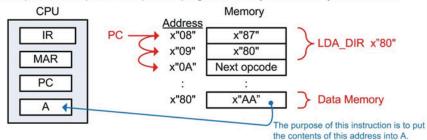

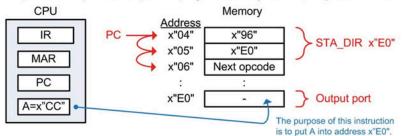

| 13.2.2 Addressing Modes                                 | 445 |

| 13.2.3 Classes of Instructions                          | 446 |

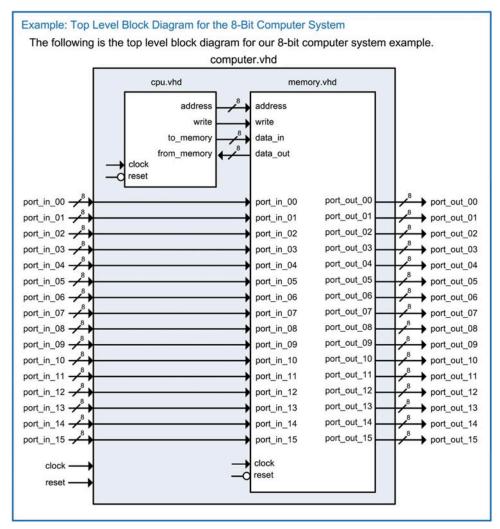

| 13.3 COMPUTER IMPLEMENTATION: AN 8-BIT COMPUTER EXAMPLE | 453 |

| 13.3.1 Top Level Block Diagram                          | 453 |

| 13.3.2 Instruction Set Design                           | 454 |

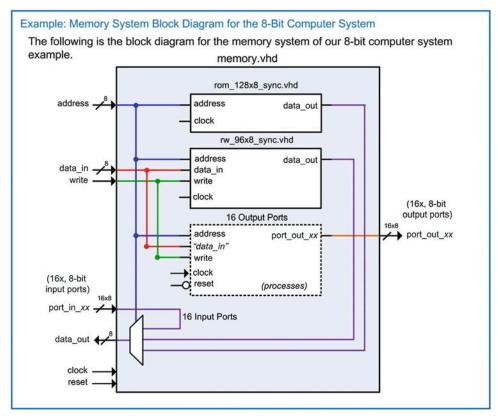

| 13.3.3 Memory System Implementation                     | 455 |

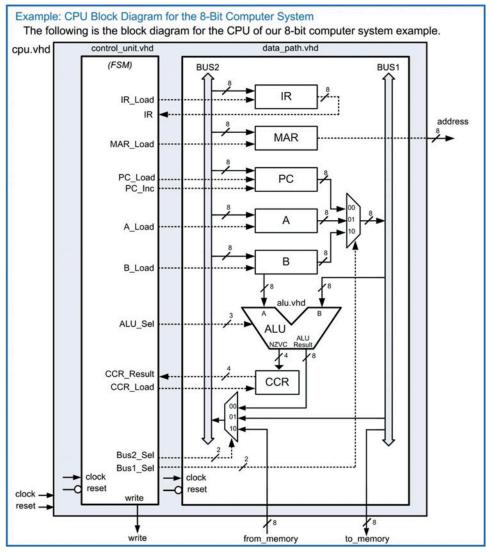

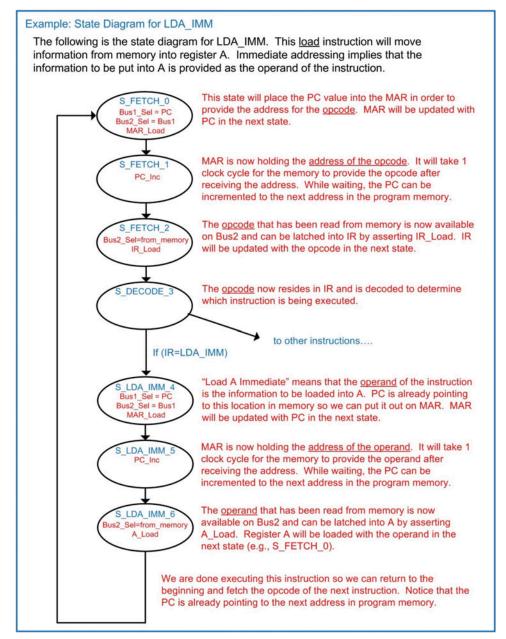

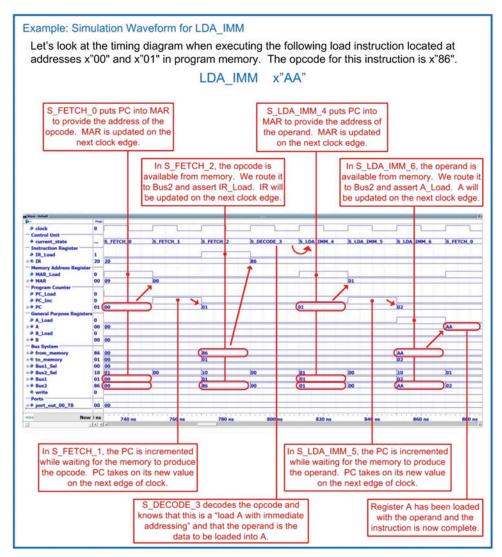

| 13.3.4 CPU Implementation                               | 460 |

| 13.4 Architecture Considerations                        | 480 |

| 13.4.1 Von Neumann Architecture                         | 480 |

| 13.4.2 Harvard Architecture                             | 480 |

| APPENDIX A: LIST OF WORKED EXAMPLES                     | 487 |

| APPENDIX B: CONCEPT CHECK SOLUTIONS                     | 493 |

| INDEX                                                   | 495 |

## Chapter 1: Introduction: Analog vs. Digital

We often hear that we live in a digital age. This refers to the massive adoption of computer systems within every aspect of our lives from smartphones to automobiles to household appliances. This statement also refers to the transformation that has occurred to our telecommunications infrastructure that now transmits voice, video, and data using 1's and 0's. There are a variety of reasons that digital systems have become so prevalent in our lives. In order to understand these reasons, it is good to start with an understanding of what a digital system is and how it compares to its counterpart, the analog system. The goal of this chapter is to provide an understanding of the basic principles of analog and digital systems.

Learning Outcomes—After completing this chapter, you will be able to:

- 1.1 Describe the fundamental differences between analog and digital systems.

- 1.2 Describe the advantages of digital systems compared to analog systems.

#### 1.1 Differences Between Analog and Digital Systems

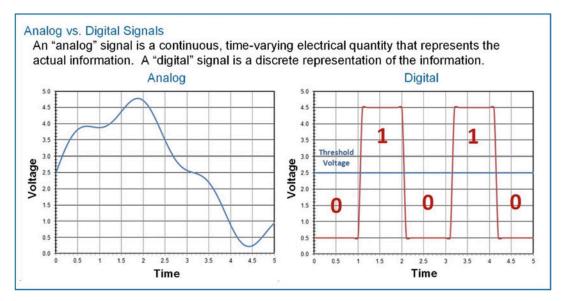

Let's begin by looking at signaling. In electrical systems, signals represent information that is transmitted between devices using an electrical quantity (voltage or current). An analog signal is defined as a continuous, time-varying quantity that corresponds directly to the information it represents. An example of this would be a barometric pressure sensor that outputs an electrical voltage corresponding to the pressure being measured. As the pressure goes up, so does the voltage. While the range of the input (pressure) and output (voltage) will have different spans, there is a direct mapping between the pressure and voltage. Another example would be sound striking a traditional analog microphone. Sound is a pressure wave that travels through a medium such as air. As the pressure wave strikes the diaphragm in the microphone, the diaphragm moves back and forth. Through the process of inductive coupling, this movement is converted to an electric current. The characteristics of the current signal produced (e.g., frequency and magnitude) correspond directly to the characteristics of the incoming sound wave. The current can travel down a wire and go through another system that works in the opposite manner by inductively coupling the current onto another diaphragm, which in turn moves back and forth forming a pressure wave and thus sound (i.e., a speaker or earbud). In both of these examples, the electrical signal represents the actual information that is being transmitted and is considered analog. Analog signals can be represented mathematically as a function with respect to time.

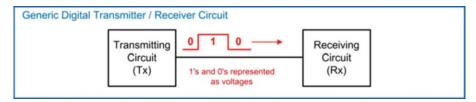

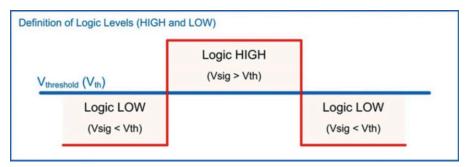

In digital signaling the electrical signal itself is not directly the information it represents; instead, the information is encoded. The most common type of encoding is binary (1's and 0's). The 1's and 0's are represented by the electrical signal. The simplest form of digital signaling is to define a threshold voltage directly in the middle of the range of the electrical signal. If the signal is above this threshold, the signal is representing a 1. If the signal is below this threshold, the signal is representing a 0. This type of signaling is not considered continuous as in analog signaling; instead, it is considered to be *discrete* because the information is transmitted as a series of distinct values. The signal transitions between a 1 to 0 and 0 to 1 are assumed to occur instantaneously. While this is obviously impossible, for the purposes of information transmission, the values can be interpreted as a series of discrete values. This is a *digital* signal and is not the actual information but rather the binary encoded representation of the original information. Digital signals are not represented using traditional mathematical functions; instead, the digital values are typically held in tables of 1's and 0's.

**Examples of Analog Signals and Systems**: The human interface to a computer; the electrical signal representing sound that travels down the wire of a set of headphones; the actual sound coming out of headphones; electricity coming out of a wall outlet; the voltage from a battery or solar cell.

**Examples of Digital Signals and Systems**: Information stored on a computer; the computer hardware that processes information; devices such as computers, tablets, and smartphones are also considered digital systems because their hardware and information being processed are digital; the information being transmitted over the Internet and wireless networks is digital.

Figure 1.1 shows an example analog signal (left) and an example digital signal (right). While the digital signal is in reality continuous, it represents a series of discrete 1 and 0 values.

Fig. 1.1

Analog (left) vs. digital (right) signals

#### CONCEPT CHECK

- CC1.1 If a digital signal is only a discrete representation of real information, how is it possible to produce high quality music without hearing "gaps" in the output due to the digitization process?

- A) The gaps are present, but they occur so quickly that the human ear can't detect them.

- B) When the digital music is converted back to analog sound the gaps are smoothed out since an analog signal is by definition *continuous*.

- C) Digital information is a continuous, time-varying signal so there aren't gaps.

- D) The gaps can be heard if the music is played slowly, but at normal speed, they can't be.

#### 1.2 Advantages of Digital Systems over Analog Systems

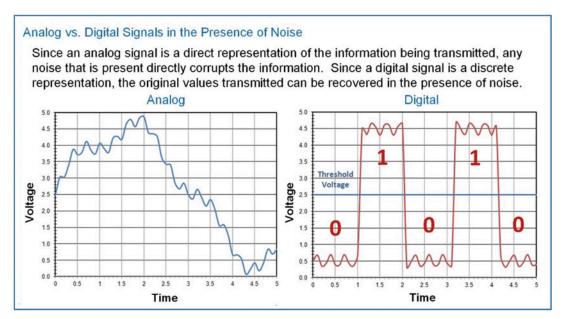

There are a variety of reasons that digital systems are preferred over analog systems. First is their ability to operate within the presence of noise. Since an analog signal is a direct representation of the physical quantity it is transmitting, any noise that is coupled onto the electrical signal is interpreted as noise on the original physical quantity. An example of this is when you are listening to an AM/FM radio and you hear distortion of the sound coming out of the speaker. The distortion you hear is not due to actual distortion of the music as it was played at the radio station but rather electrical noise that was coupled onto the analog signal transmitted to your radio prior to being converted back into sound by the speakers. Since the signal in this case is analog, the speaker simply converts it in its entirety (noise + music) into sound. In the case of digital signaling, a significant amount of noise can be added to the signal while still preserving the original 1's and 0's that are being transmitted. For example, if the signal is representing a 0, the receiver will still interpret the signal as a 0 as long as the noise doesn't cause the level to exceed the threshold. Once the receiver interprets the signal as a 0, it stores the encoded value as a 0 thus ignoring any noise present during the original transmission. Figure 1.2 shows the exact same noise added to the analog and digital signals from Fig. 1.1. The analog signal is distorted; however, the digital signal is still able to transmit the 0's and 1's that represent the information.

Fig. 1.2

Noise on analog (left) and digital (right) signals

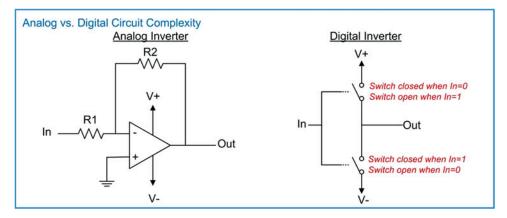

Another reason that digital systems are preferred over analog ones is the simplicity of the circuitry. In order to produce a 1 and 0, you simply need an electrical switch. If the switch connects the output to a voltage below the threshold, then it produces a 0. If the switch connects the output to a voltage above the threshold, then it produces a 1. It is relatively simple to create such a switching circuit using modern transistors. Analog circuitry, however, needs to perform the conversion of the physical quantity it is representing (e.g., pressure, sound) into an electrical signal all the while maintaining a direct correspondence between the input and output. Since analog circuits produce a direct, continuous representation of information, they require more complicated designs to achieve linearity in the presence of environmental variations (e.g., power supply, temperature, fabrication differences). Since digital circuits only produce a discrete representation of the information, they can be implemented with simple switches that are only

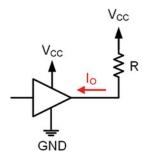

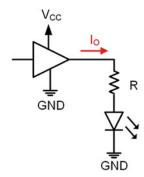

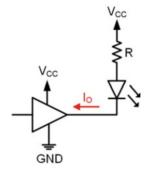

altered when information is produced or retrieved. Figure 1.3 shows an example comparison between an analog inverting amplifier and a digital inverter. The analog amplifier uses dozens of transistors (inside the triangle) and two resistors to perform the inversion of the input. The digital inverter uses two transistors that act as switches to perform the inversion.

Fig. 1.3

Analog (left) vs. digital (right) circuits

A final reason that digital systems are being widely adopted is their reduced power consumption. With the advent of complementary metal oxide transistors (CMOS), electrical switches can be created that consume very little power to *turn* on or off and consume relatively negligible amounts of power to *keep* on or off. This has allowed large-scale digital systems to be fabricated without excessive levels of power consumption. For stationary digital systems such as servers and workstations, extremely large and complicated systems can be constructed that consume reasonable amounts of power. For portable digital systems such as smartphones and tablets, this means useful tools can be designed that are able to run on portable power sources. Analog circuits, on the other hand, require continuous power to accurately convert and transmit the electrical signal representing the physical quantity. Also, the circuit techniques that are required to compensate for variances in power supply and fabrication processes in analog systems require additional power consumption. For these reasons, analog systems are being replaced with digital systems wherever possible to exploit their noise immunity, simplicity, and low power consumption. While analog systems will always be needed at the transition between the physical (e.g., microphones, camera lenses, sensors, video displays) and the electrical world, it is anticipated that the push toward digitization of everything in between (e.g., processing, transmission, storage) will continue.

#### CONCEPT CHECK

- CC1.2 When does the magnitude of electrical noise on a digital signal prevent the original information from being determined?

- A) When it causes the system to draw too much power.

- B) When the shape of the noise makes the digital signal look smooth and continuous like a sine wave.

- C) When the magnitude of the noise is large enough that it causes the signal to inadvertently cross the threshold voltage.

- D) It doesn't. A digital signal can withstand any magnitude of noise.

5

#### Summary

- An analog system uses a direct mapping between an electrical quantity and the information being processed. A digital system, on the other hand, uses a discrete representation of the information.

- Using a discrete representation allows the digital signals to be more immune to noise in addition to requiring simple circuits that require less power to perform the computations.

#### **Exercise Problems**

## Section 1.1: Differences Between Analog and Digital Systems

- 1.1.1 If an electrical signal is a direct function of a physical quantity, is it considered analog or digital?

- 1.1.2 If an electrical signal is a discrete representation of information, is it considered analog or digital?

- 1.1.3 What part of any system will always require an analog component?

- 1.1.4 Is the sound coming out of earbuds analog or digital?

- 1.1.5 Is the MP3 file stored on an iPod analog or digital?

- 1.1.6 Is the circuitry that reads the MP3 file from memory in an iPod analog or digital?

- 1.1.7 Is the electrical signal that travels down earphone wires analog or digital?

- 1.1.8 Is the voltage coming out of the battery in an iPod analog or digital?

- 1.1.9 Is the physical interface on the touch display of an iPod analog or digital?

- **1.1.10** Take a look around right now and identify two digital technologies in use.

- 1.1.11 Take a look around right now and identify two analog technologies in use.

- 1.1.12 Using the terminology from this chapter, describe the difference between an analog clock with a smooth moving second hand and a digital clock.

1.1.13 Using the terminology from this chapter, describe the difference between an analog and digital thermometer.

## Section 1.2: Advantages of Digital Systems over Analog Systems

- 1.2.1 Give three advantages of using digital systems over analog.

- 1.2.2 Name a technology or device that has evolved from analog to digital in your lifetime.

- 1.2.3 Name an analog technology or device that has become obsolete in your lifetime.

- 1.2.4 Name an analog technology or device that has been replaced by digital technology but is still in use due to nostalgia.

- 1.2.5 Name a technology or device invented in your lifetime that could not have been possible without digital technology.

- 1.2.6 In this chapter it was discussed that in digital circuits, a transistor is used to create a simple switch. Doing a quick internet search, about how many transistors are in a modern microprocessor?

- 1.2.7 In this chapter it was discussed that in analog circuits the circuit design is more complex and as a result, fewer transistors are used. The analog circuit shown in Fig. 1.3 is based on an analog device called an operational amplifier. Doing a quick internet search, about how many transistors are in an operational amplifier device?

### **Chapter 2: Number Systems**

Logic circuits are used to generate and transmit 1's and 0's to compute and convey information. This two-valued number system is called binary. As presented earlier, there are many advantages of using a binary system; however, the human brain has been taught to count, label, and measure using the decimal number system. The decimal number system contains 10 unique symbols (0  $\rightarrow$  9) commonly referred to as the Arabic numerals. Each of these symbols is assigned a relative magnitude to the other symbols. For example, 0 is less than 1, 1 is less than 2, etc. It is often conjectured that the 10-symbol number system that we humans use is due to the availability of our 10 fingers (or digits) to visualize counting up to 10. Regardless, our brains are trained to think of the real world in terms of a decimal system. In order to bridge the gap between the way our brains think (decimal) and how we build our computers (binary), we need to understand the basics of number systems. This includes the formal definition of a positional number system and how it can be extended to accommodate any arbitrarily large (or small) value. This also includes how to convert between different number systems that contain different numbers of symbols. In this chapter, we cover 4 different number systems: decimal (10 symbols), binary (2 symbols), octal (8 symbols), and hexadecimal (16 symbols). The study of decimal and binary is obvious as they represent how our brains interpret the physical world (decimal) and how our computers work (binary). Hexadecimal is studied because it is a useful means to represent large sets of binary values using a manageable number of symbols. Octal is rarely used but is studied as an example of how the formalization of the number systems can be applied to all systems regardless of the number of symbols they contain. This chapter will also discuss how to perform basic arithmetic in the binary number system and represent negative numbers. The goal of this chapter is to provide an understanding of the basic principles of binary number systems.

Learning Outcomes—After completing this chapter, you will be able to:

- 2.1 Describe the formation and use of positional number systems.

- 2.2 Convert numbers between different bases.

- 2.3 Perform binary addition and subtraction by hand.

- 2.4 Use two's complement numbers to represent negative numbers.

#### 2.1 Positional Number Systems

A positional number system allows the expansion of the original set of symbols so that they can be used to represent any arbitrarily large (or small) value. For example, if we use the 10 symbols in our decimal system, we can count from 0 to 9. Using just the individual symbols, we do not have enough symbols to count beyond 9. To overcome this, we use the same set of symbols but assign a different value to the symbol based on its position within the number. The *position* of the symbol with respect to other symbols in the number allows an individual symbol to represent greater (or lesser) values. We can use this approach to represent numbers larger than the original set of symbols. For example, let's say we want to count from 0 upward by 1. We begin counting from 0, 1, 2, 3, 4, 5, 6, 7, 8, to 9. When we are out of symbols and wish to go higher, we bring on a symbol in a different position with that position being valued higher and then start counting over with our original symbols (e.g., ..., 9, 10, 11,... 19, 20, 21,...). This is repeated each time a position runs out of symbols (e.g., ..., 99, 100, 101... 999, 1000, 1001,...).

First, let's look at the formation of a number system. The first thing that is needed is a set of symbols. The formal term for one of the symbols in a number system is a *numeral*. One or more numerals are used to form a *number*. We define the number of numerals in the system using the terms *radix* or *base*. For

example, our decimal number system is said to be *base 10* or have a *radix of 10* because it consists of 10 unique numerals or symbols.

#### Radix = Base $\equiv$ the number of numerals in the number system

The next thing that is needed is the relative value of each numeral with respect to the other numerals in the set. We can say 0 < 1 < 2 < 3 etc. to define the relative magnitudes of the numerals in this set. The numerals are defined to be greater or less than their neighbors by a magnitude of 1. For example, in the decimal number system, each of the subsequent numerals is greater than its predecessor by exactly 1. When we define this relative magnitude, we are defining that the numeral 1 is greater than the numeral 0 by a magnitude of 1; the numeral 2 is greater than the numeral 1 by a magnitude of 1, etc. At this point we have the ability to count from 0 to 9 by 1's. We also have the basic structure for mathematical operations that have results that fall within the numeral set from 0 to 9 (e.g., 1 + 2 = 3). In order to expand the values that these numerals can represent, we need define the rules of a positional number system.

#### 2.1.1 Generic Structure

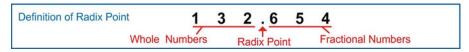

In order to represent larger or smaller numbers than the lone numerals in a number system can represent, we adopt a positional system. In a positional number system, the relative position of the numeral within the overall number dictates its value. When we begin talking about the position of a numeral, we need to define a location to which all of the numerals are positioned with respect to. We define the *radix point* as the point within a number to which numerals to the left represent whole numbers and numerals to the right represent fractional numbers. The radix point is denoted with a period (i.e., "."). A particular number system often renames this radix point to reflect its base. For example, in the base 10 number system (i.e., decimal), the radix point is commonly called the *decimal point*; however, the term *radix point* can be used across all number systems as a generic term. If the radix point is not present in a number, it is assumed to be to the right of number. Fig. 2.1 shows an example number highlighting the radix point and the relative positions of the whole and fractional numerals.

Fig. 2.1

Definition of radix point

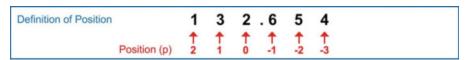

Next, we need to define the position of each numeral with respect to the radix point. The position of the numeral is assigned a whole number with the number to the left of the radix point having a position value of 0. The position number increases by 1 as numerals are added to the left (2, 3, 4...) and decreased by 1 as numerals are added to the right (-1, -2, -3). We will use the variable p to represent position. The position number will be used to calculate the value of each numeral in the number based on its relative position to the radix point. Figure 2.2 shows the example number with the position value of each numeral highlighted.

**Fig. 2.2** Definition of position number (p) within the number

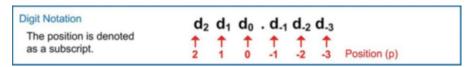

In order to create a generalized format of a number, we assign the term *digit* (d) to each of the numerals in the number. The term digit signifies that the numeral has a position. The position of the digit within the number is denoted as a subscript. The term *digit* can be used as a generic term to describe a numeral across all systems, although some number systems will use a unique term instead of digit which indicates its base. For example, the binary system uses the term *bit* instead of digit; however, using the term digit to describe a generic numeral in any system is still acceptable. Figure 2.3 shows the generic subscript notation used to describe the position of each digit in the number.

Fig. 2.3

Digit notation

We write a number from left to right starting with the highest position digit that is greater than 0 and end with the lowest position digit that is greater than 0. This reduces the number of numerals that are written; however, a number can be represented with an arbitrary number of 0's to the left of the highest position digit greater than 0 and an arbitrary number of 0's to the right of the lowest position digit greater than 0 without affecting the value of the number. For example, the number 132.654 could be written as 0132.6540 without affecting the value of the number. The 0's to the left of the number are called *leading 0's* and the 0's to the right of the number are called *trailing 0's*. The reason this is being stated is because when a number is implemented in circuitry, the number of numerals is fixed, and each numeral must have a value. The variable n is used to represent the number of numerals in a number. If a number is defined with n = 4, that means 4 numerals are always used. The number 0 would be represented as 0000 with both representations having an equal value.

#### 2.1.2 Decimal Number System (Base 10)

As mentioned earlier, the decimal number system contains ten unique numerals (0, 1, 2, 3, 4, 5, 6, 7, 8,and 9). This system is thus a base 10 or a radix 10 system. The relative magnitudes of the symbols are 0 < 1 < 2 < 3 < 4 < 5 < 6 < 7 < 8 < 9.

#### 2.1.3 Binary Number System (Base 2)

The binary number system contains two unique numerals (0 and 1). This system is thus a base 2 or a radix 2 system. The relative magnitudes of the symbols are 0 < 1. At first glance, this system looks very limited in its ability to represent large numbers due to the small number of numerals. When counting up, as soon as you count from 0 to 1, you are out of symbols and must increment the p + 1 position in order to represent the next number (e.g.,  $0, 1, 10, 11, 100, 101, \ldots$ ); however, magnitudes of each position scale quickly so that circuits with a reasonable amount of digits can represent very large numbers. The term bit is used instead of digit in this system to describe the individual numerals and at the same time indicate the base of the number.

Due to the need for multiple bits to represent meaningful information, there are terms dedicated to describing the number of bits in a group. When 4 bits are grouped together, they are called a **nibble**. When 8 bits are grouped together, they are called a **byte**. Larger groupings of bits are called **words**. The size of the word can be stated as either an *n-bit word* or omitted if the size of the word is inherently implied. For example, if you were using a 32-bit microprocessor, using the term *word* would be

interpreted as a 32-bit word. For example, if there was a 32-bit grouping, it would be referred to as a 32-bit word. The leftmost bit in a binary number is called the **most significant bit** (MSB). The rightmost bit in a binary number is called the **least significant bit** (LSB).

#### 2.1.4 Octal Number System (Base 8)

The octal number system contains eight unique numerals (0, 1, 2, 3, 4, 5, 6, 7). This system is thus a base 8 or a radix 8 system. The relative magnitudes of the symbols are 0 < 1 < 2 < 3 < 4 < 5 < 6 < 7. We use the generic term *digit* to describe the numerals within an octal number.

#### 2.1.5 Hexadecimal Number System (Base 16)

The hexadecimal number system contains 16 unique numerals. This system is most often referred to in spoken word as "hex" for short. Since we only have ten Arabic numerals in our familiar decimal system, we need to use other symbols to represent the remaining six numerals. We use the alphabetic characters A–F in order to expand the system to 16 numerals. The 16 numerals in the hexadecimal system are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F. The relative magnitudes of the symbols are 0 < 1 < 2 < 3 < 4 < 5 < 6 < 7 < 8 < 9 < A < B < C < D < E < F. We use the generic term digit to describe the numerals within a hexadecimal number.

At this point, it becomes necessary to indicate the base of a written number. The number 10 has an entirely different value if it is a decimal number or binary number. In order to handle this, a subscript is typically included at the end of the number to denote its base. For example,  $10_{10}$  indicates that this number is decimal "ten." If the number was written as  $10_2$ , this number would represent binary "one zero." Table 2.1 lists the equivalent values in each of the four number systems just described for counts from  $0_{10}$  to  $15_{10}$ . The left side of the table does not include leading 0 s. The right side of the table contains the same information but includes the leading zeros. The equivalencies of decimal, binary, and hexadecimal in this table are typically committed to memory.

| Decimal     | Binary | Octal  | Hex         | Decimal | Binary | Octal | Hex         |

|-------------|--------|--------|-------------|---------|--------|-------|-------------|

| 0           | 0      | 0      | 0           | 00      | 0000   | 00    | 0           |

| 1           | 1      | 1      | 1           | 01      | 0001   | 01    | 1           |

| 2           | 10     | 2      | 2           | 02      | 0010   | 02    | 2           |

| 3           | 11     | 3      | 3           | 03      | 0011   | 03    | 3           |

| 4           | 100    | 4      | 4           | 04      | 0100   | 04    | 4           |

| 5           | 101    | 5<br>6 | 5           | 05      | 0101   | 05    | 5           |

| 5<br>6<br>7 | 110    | 6      | 5<br>6<br>7 | 06      | 0110   | 06    | 5<br>6<br>7 |

| 7           | 111    | 7      | 7           | 07      | 0111   | 07    | 7           |

| 8           | 1000   | 10     | 8           | 08      | 1000   | 10    | 8           |

| 9           | 1001   | 11     | 9           | 09      | 1001   | 11    | 9           |

| 10          | 1010   | 12     | 9<br>A<br>B | 10      | 1010   | 12    | 9<br>A<br>B |

| 11          | 1011   | 13     | В           | 11      | 1011   | 13    | В           |

| 12          | 1100   | 14     | С           | 12      | 1100   | 14    | С           |

| 13          | 1101   | 15     |             | 13      | 1101   | 15    | D           |

| 14          | 1110   | 16     | D<br>E<br>F | 14      | 1110   | 16    | D<br>E<br>F |

| 15          | 1111   | 17     | F           | 15      | 1111   | 17    | F           |

**Table 2.1**Number system equivalency

#### CONCEPT CHECK

CC2.1 The base of a number system is arbitrary and is commonly selected to match a particular aspect of the physical system in which it is used (e.g., base 10 corresponds to our 10 fingers, base 2 corresponds to the 2 states of a switch). If a physical system contained 3 unique modes and a base of 3 was chosen for the number system, what is the base 3 equivalent of the decimal number 3?

A)

$$3_{10} = 11_3$$

B)

$$3_{10} = 3_3$$

C)

$$3_{10} = 10_3$$

D)  $3_{10} = 21_3$

D)

$$3_{10} = 21_3$$

#### 2.2 Base Conversion

Now we look at converting between bases. There are distinct techniques for converting to and from decimal. There are also techniques for converting between bases that are powers of 2 (e.g., base 2, 4, 8, 16, etc.).

#### 2.2.1 Converting to Decimal

The value of each digit within a number is based on the individual digit value and the digit's position. Each position in the number contains a different weight based on its relative location to the radix point. The weight of each position is based on the radix of the number system that is being used. The weight of each position in decimal is defined as:

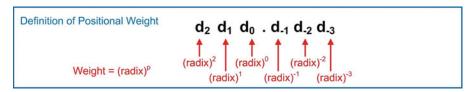

$$\textbf{Weight} = (\textbf{Radix})^{\textbf{p}}$$

This expression gives the number system the ability to represent fractional numbers since an expression with a negative exponent (e.g., x<sup>-y</sup>) is evaluated as one over the expression with the exponent change to positive (e.g.,  $1/x^{y}$ ). Figure 2.4 shows the generic structure of a number with its positional weight highlighted.

Fig. 2.4 Weight definition

In order to find the decimal value of each of the numerals in the number, its individual numeral value is multiplied by its positional weight. In order to find the value of the entire number, each value of the individual numeral-weight products is summed. The generalized format of this conversion is written as:

$$\textit{Total Decimal Value} = \sum_{i=o_{-i-}}^{p_{\max}} \textbf{d}_i \cdot (\textit{radix})^i$$

In this expression,  $p_{max}$  represents the highest position number that contains a numeral greater than 0. The variable  $p_{min}$  represents the lowest position number that contains a numeral greater than 0. These limits are used to simplify the hand calculations; however, these terms theoretically could be  $+\infty$  to  $-\infty$  with no effect on the result since the summation of every leading 0 and every trailing 0 contributes nothing to the result.

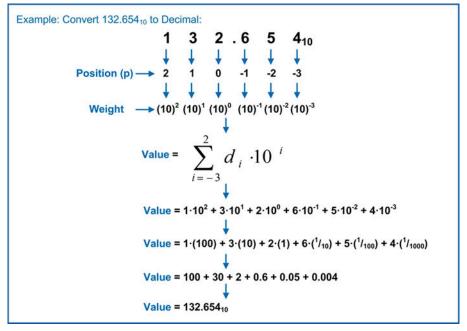

As an example, let's evaluate this expression for a decimal number. The result will yield the original number but will illustrate how positional weight is used. Let's take the number  $132.654_{10}$ . To find the decimal value of this number, each numeral is multiplied by its positional weight, and then all of the products are summed. The positional weight for the digit 1 is  $(radix)^p$  or  $(10)^2$ . In decimal this is called the hundred's position. The positional weight for the digit 3 is  $(10)^1$ , referred to as the ten's position. The positional weight for digit 2 is  $(10)^0$ , referred to as the one's position. The positional weight for digit 6 is  $(10)^{-1}$ , referred to as the tenth's position. The positional weight for digit 5 is  $(10)^{-2}$ , referred to as the hundredth's position. The positional weight for digit 4 is  $(10)^{-3}$ , referred to as the thousandth's position.

When these weights are multiplied by their respective digits and summed, the result is the original decimal number 132.654<sub>10</sub>. Example 2.1 shows this process step-by-step.

Example 2.1

Converting decimal to decimal

This process is used to convert between any other base to decimal.

#### 2.2.1.1 Binary to Decimal

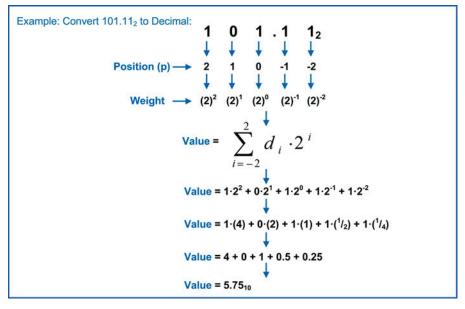

Let's convert  $101.11_2$  to decimal. The same process is followed with the exception that the base in the summation is changed to 2. Converting from binary to decimal can be accomplished quickly in your head due to the fact that the bit values in the products are either 1 or 0. That means any bit that is a 0 has no impact on the outcome and any bit that is a 1 simply yields the weight of its position. Example 2.2 shows the step-by-step process converting a binary number to decimal.

Example 2.2 Converting binary to decimal

#### 2.2.1.2 Octal to Decimal

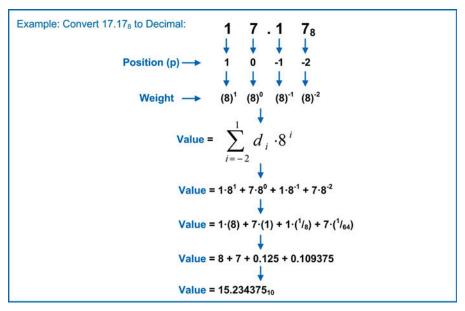

When converting from octal to decimal, the same process is followed with the exception that the base in the weight is changed to 8. Example 2.3 shows an example of converting an octal number to decimal.

Example 2.3 Converting octal to decimal

#### 2.2.1.3 Hexadecimal to Decimal

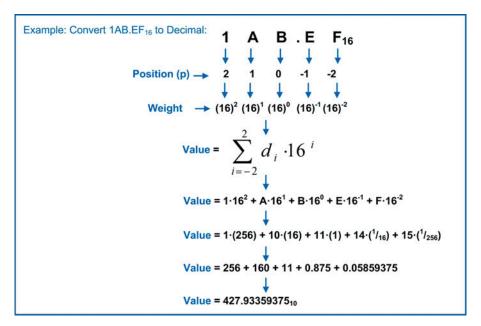

Let's convert 1AB.EF<sub>16</sub> to decimal. The same process is followed with the exception that the base is changed to 16. When performing the conversion, the decimal equivalent of the numerals A–F needs to be used. Example 2.4 shows the step-by-step process converting a hexadecimal number to decimal.

**Example 2.4**Converting hexadecimal to decimal

In some cases, it is desired to specify a *level of accuracy* for the conversion in order to bound the number of fractional digits in the final result. For example, if the conversion in Example 2.4 was stated as "convert 1AB.EF<sub>16</sub> to decimal with a <u>fractional accuracy of 2 digits</u>," the final result would be 427.93<sub>10</sub>. How rounding is handled can also be specified with the two options being *with* or *without rounding*. In the case where the conversion is performed <u>with rounding</u>, additional fractional digits may need to be computed to determine if the least significant digit of the new decimal fraction needs to be altered. For example, let's say the conversion in Example 2.4 is stated as "convert 1AB.EF<sub>16</sub> to decimal with a fractional accuracy of <u>4 digits with rounding</u>." In this case, the final result would be 427.9336<sub>10</sub>. Notice how rounding was applied to the digit in position p = -3 changing it from a 5 to a 6 based on the value in position p = -4. Now let's say the conversion in Example 2.4 is stated as "convert 1AB.EF<sub>16</sub> to decimal with a fractional accuracy of <u>4 digits without rounding</u>." In this case, the final result would be 427.9335<sub>10</sub>. Notice how without rounding simply drops all of the digits beyond the specified level of accuracy.

#### 2.2.2 Converting from Decimal

The process of converting from decimal to another base consists of two separate algorithms. There is one algorithm for converting the whole number portion of the number and another algorithm for converting the fractional portion of the number. The process for converting the whole number portion is to divide the decimal number by the base of the system you wish to convert to. The division will result in a quotient and a whole number remainder. The remainder is recorded as the *least significant numeral* in the converted number. The resulting quotient is then divided again by the base, which results in a new quotient and new remainder. The remainder is recorded as the next higher order numeral in the new number. This process is repeated until a quotient of 0 is achieved. At that point the conversion is complete. The remainders will always be within the numeral set of the base being converted to.

The process for converting the fractional portion is to multiply just the fractional component of the number by the base. This will result in a product that contains a whole number and a fraction. The whole number is recorded as the *most significant digit* of the new converted number. The new fractional portion is then multiplied again by the base with the whole number portion being recorded as the next lower order numeral. This process is repeated until the product yields a fractional component equal to zero or the desired level of accuracy has been achieved. The level of accuracy is specified by the number of numerals in the new converted number. For example, the conversion would be stated as "convert this decimal number to binary with a fractional accuracy of 4 bits." This means the final result would only have 4 bits in the fraction. In cases where the conversion does not yield exactly 4 fractional bits, there are two approaches that can be used. The first is to have *no rounding*, which means the conversion simply stops at the desired accuracy. The second is to apply *rounding*, which means additional bits beyond the desired accuracy are computed in order to determine whether the least significant bit reported.

#### 2.2.2.1 Decimal to Binary

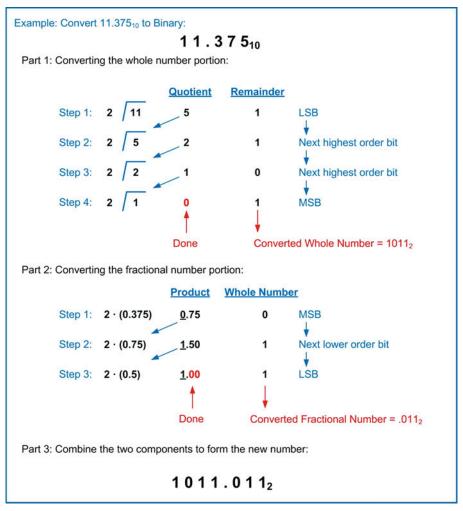

Let's convert 11.375<sub>10</sub> to binary. Example 2.5 shows the step-by-step process converting a decimal number to binary.

**Example 2.5**Converting decimal to binary

In many binary conversions to binary, the number of fractional bits that result from the conversion is more than needed. In this case, rounding is applied to limit the fractional accuracy. The simplest rounding approach for binary numbers is to continue the conversion for one more bit beyond the desired fractional accuracy. If the next bit is a 0, then you leave the fractional component of the number as is. If the next bit is a 1, you round the least significant bit of your number up. Often this rounding will result in a cascade of roundings from the LSB to the MSB. As an example, let's say that the conversion in Example 2.5 was specified to have a fractional accuracy of 2 bits. If the bit in position p = -3 was a 0 (which it is not, but let's just say it is for the sake of this example), then the number would be left as is, and the final converted number would be  $1011.01_2$ . However, if the bit in position p = -3 was a 1 (as it actually is in Example 2.5), then we would need to apply rounding. We would start with the bit in position p = -2. Since it is a 1, we would round that up to a 0, but we would need to apply the overflow of this rounding to the next higher order bit in position p = -1. That would then cause the value of p = -1 to go from a 0 to a 1. The final result of the conversion with rounding would be  $1011.10_2$ .

#### 2.2.2.2 Decimal to Octal

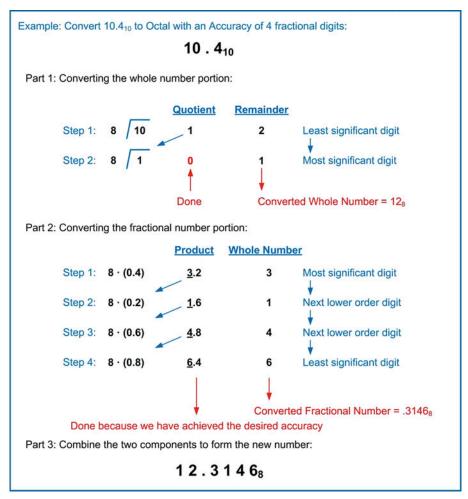

Let's convert  $10.4_{10}$  to octal with an accuracy of 4 fractional digits. When converting the fractional component of the number, the algorithm is continued until 4 digits worth of fractional numerals has been achieved. Once the accuracy has been achieved, the conversion is finished even though a product with a zero fractional value has not been obtained. Example 2.6 shows the step-by-step process converting a decimal number to octal with a fractional accuracy of 4 digits.

**Example 2.6**Converting decimal to octal

Rounding of octal digits uses a similar approach as when rounding decimal numbers, with the exception that the middle of the range of the numbers lies between digits  $3_8$  and  $4_8$ . This means that any number to be rounded that is  $4_8$  or greater will be rounded up. Numbers that are  $3_8$  or less will be rounded down, which means the fractional component of the converted number is left as in.

#### 2.2.2.3 Decimal to Hexadecimal

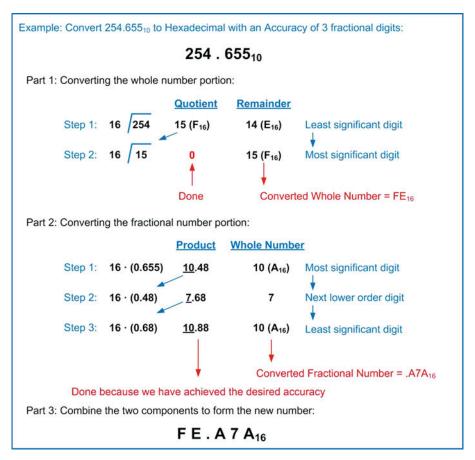

Let's convert  $254.655_{10}$  to hexadecimal with an accuracy of 3 fractional digits. When doing this conversion, all of the divisions and multiplications are done using decimal. If the results end up between  $10_{10}$  and  $15_{10}$ , then the decimal numbers are substituted with their hex symbol equivalent (i.e., A to F). Example 2.7 shows the step-by-step process of converting a decimal number to hex with a fractional accuracy of 3 digits.

**Example 2.7**Converting decimal to hexadecimal

Rounding of hexadecimal digits uses a similar approach as when rounding decimal numbers, with the exception that the middle of the range of the numbers lies between digits  $7_{16}$  and  $8_{16}$ . This means that any number to be rounded that is  $8_{16}$  or greater will be rounded up. Numbers that are  $7_{16}$  or less will be rounded down, which means the fractional component of the converted number is left as in.

#### 2.2.3 Converting Between 2<sup>n</sup> Bases

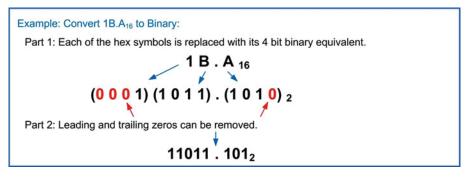

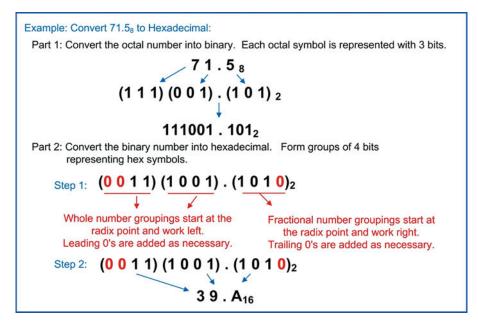

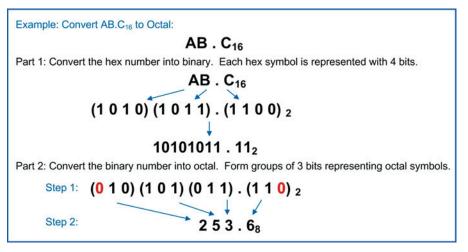

Converting between  $2^n$  bases (e.g., 2, 4, 8, 16, etc.) takes advantage of the direct mapping that each of these bases has back to binary. Base 8 numbers take exactly 3 binary bits to represent all 8 symbols (i.e.,  $0_8 = 000_2$ ,  $7_8 = 111_2$ ). Base 16 numbers take exactly 4 binary bits to represent all 16 symbols (i.e.,  $0_{16} = 0000_2$ ,  $0_{16} = 1111_2$ ).

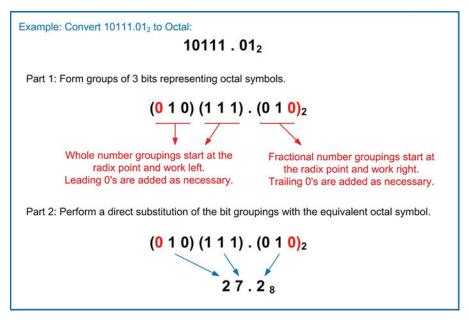

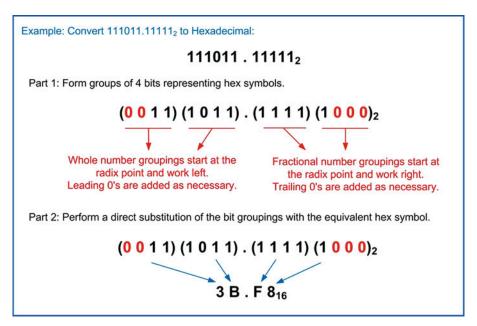

When converting *from* binary to any other 2<sup>n</sup> base, the whole number bits are grouped into the appropriate-sized sets starting from the radix point and working left. If the final leftmost grouping does not have enough symbols, it is simply padded on the left with leading 0's. Each of these groups is then directly substituted with their 2<sup>n</sup> base symbol. The fractional number bits are also grouped into the appropriate-sized sets starting from the radix point, but this time working right. Again, if the final rightmost grouping does not have enough symbols, it is simply padded on the right with trailing 0's. Each of these groups is then directly substituted with their 2<sup>n</sup> base symbol.

#### 2.2.3.1 Binary to Octal

Example 2.8 shows the step-by-step process of converting a binary number to octal.

**Example 2.8**Converting binary to octal

#### 2.2.3.2 Binary to Hexadecimal

Example 2.9 shows the step-by-step process of converting a binary number to hexadecimal.

**Example 2.9**Converting binary to hexadecimal

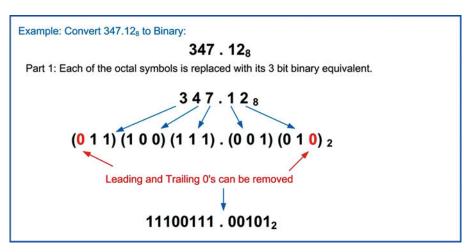

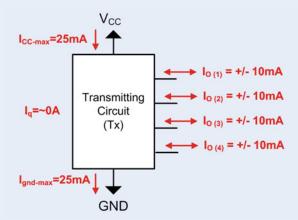

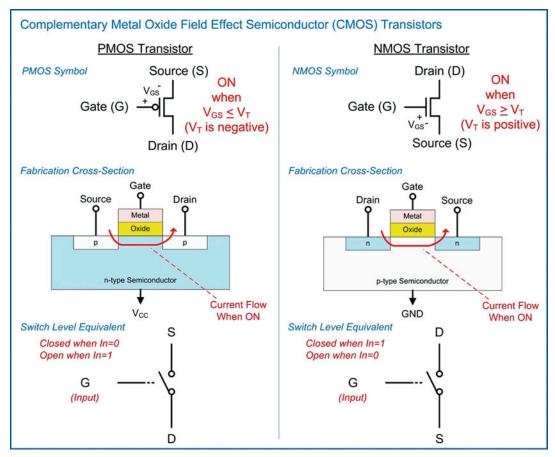

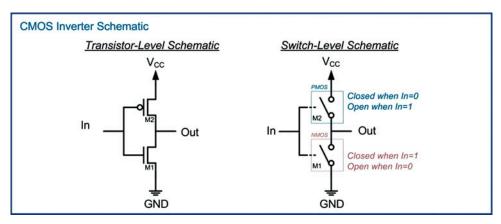

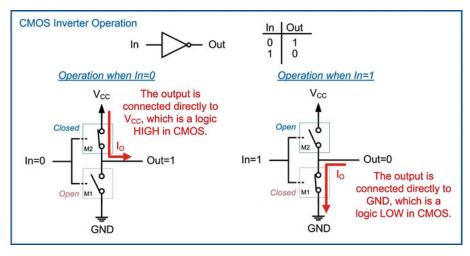

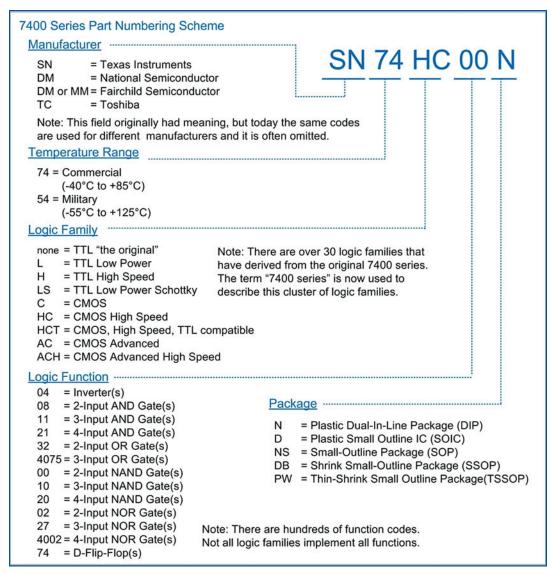

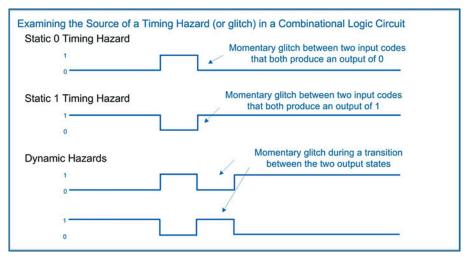

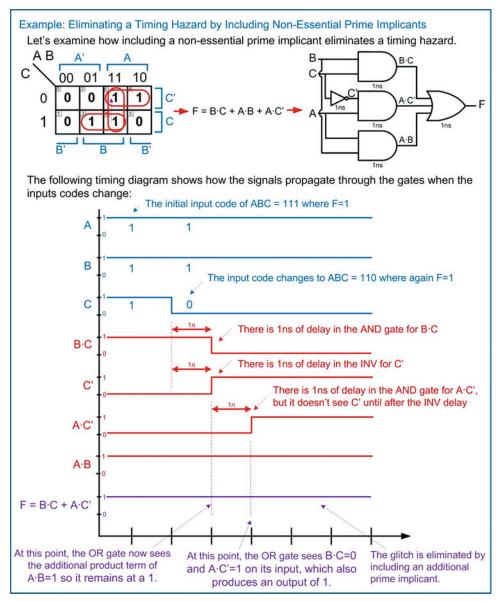

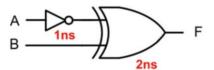

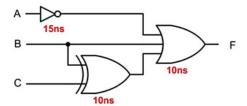

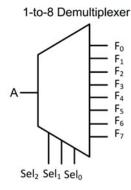

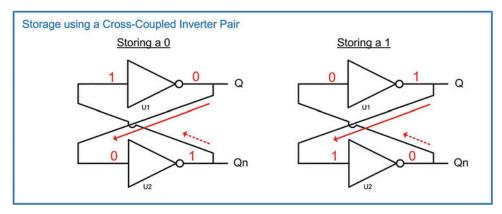

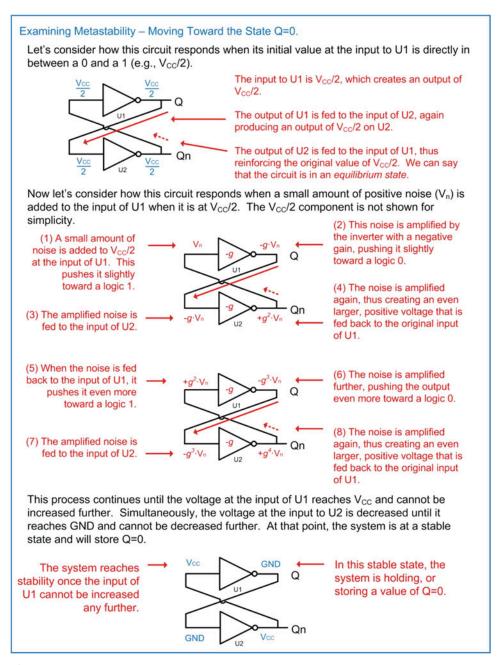

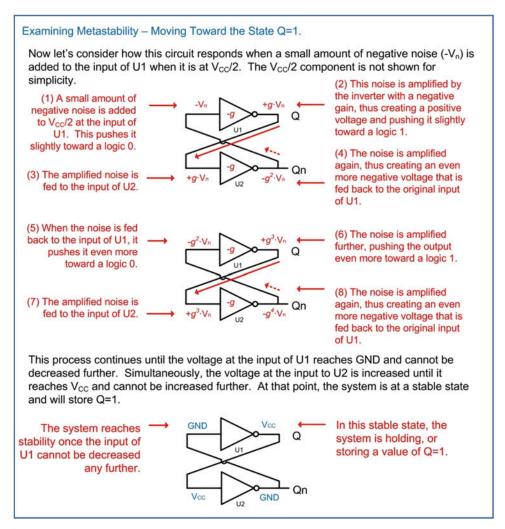

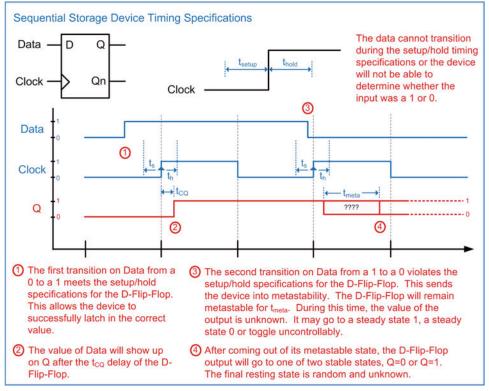

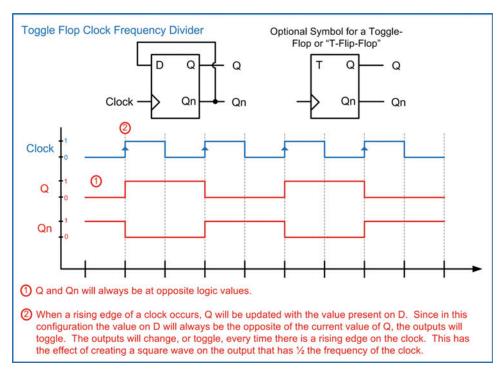

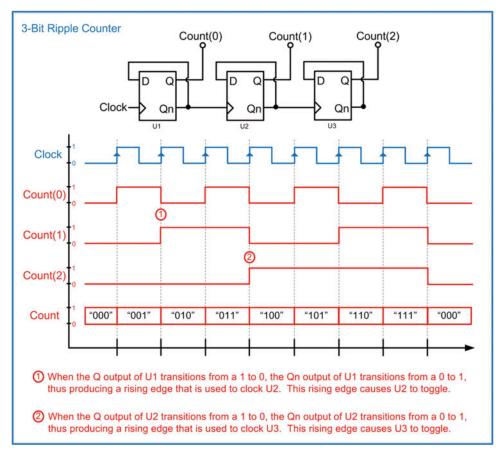

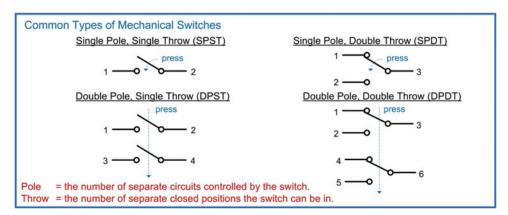

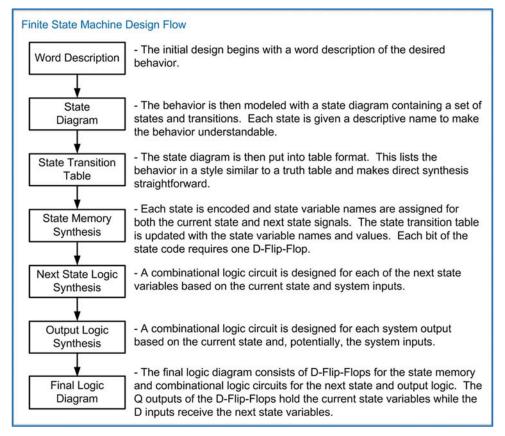

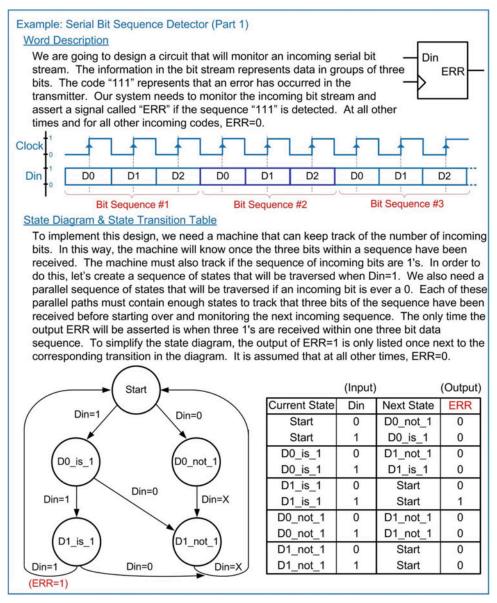

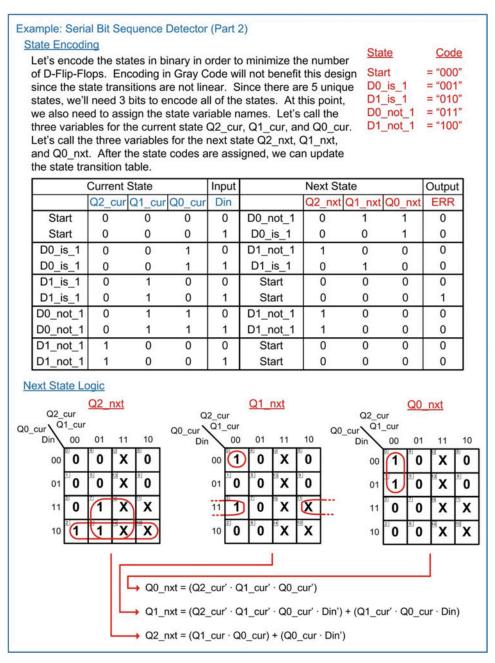

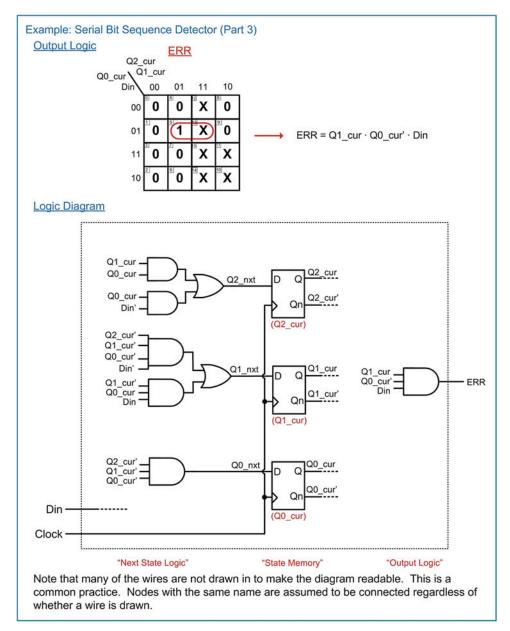

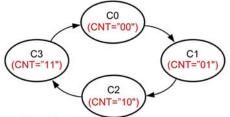

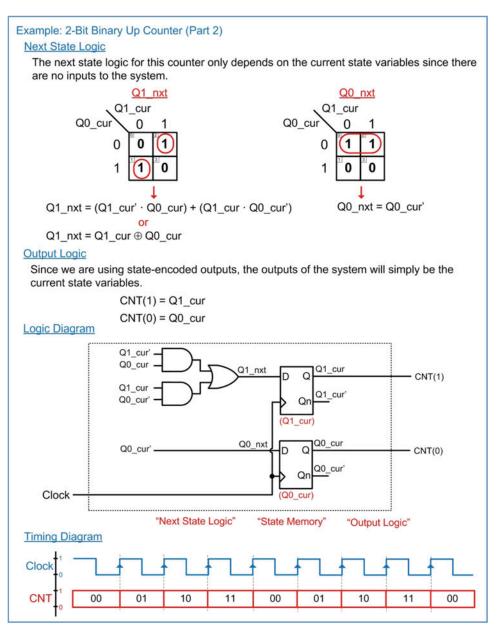

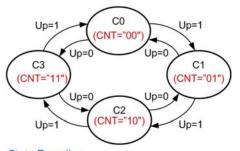

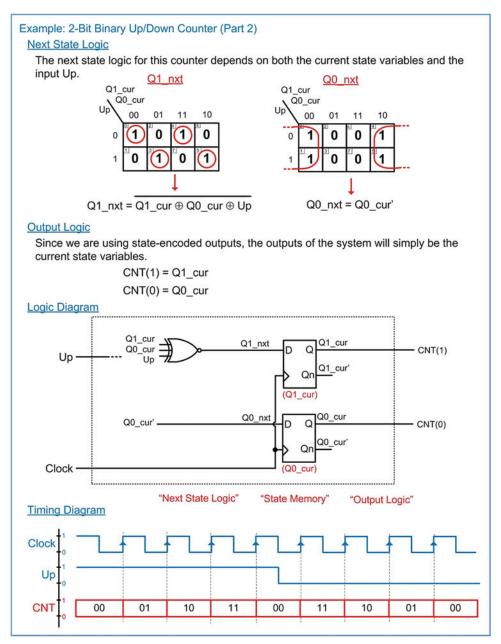

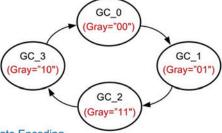

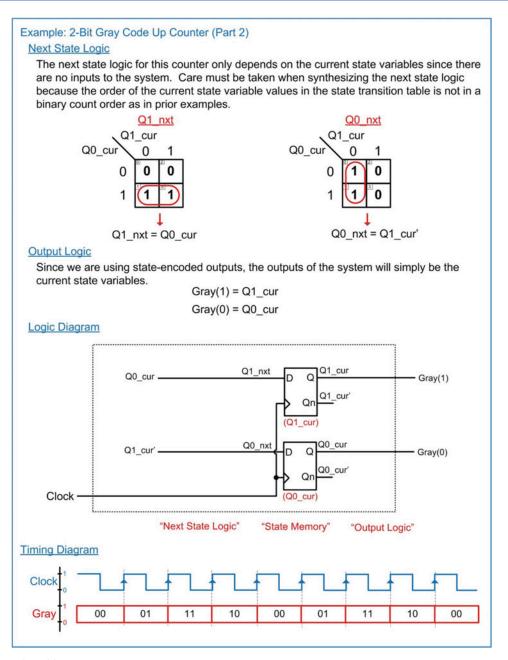

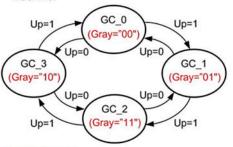

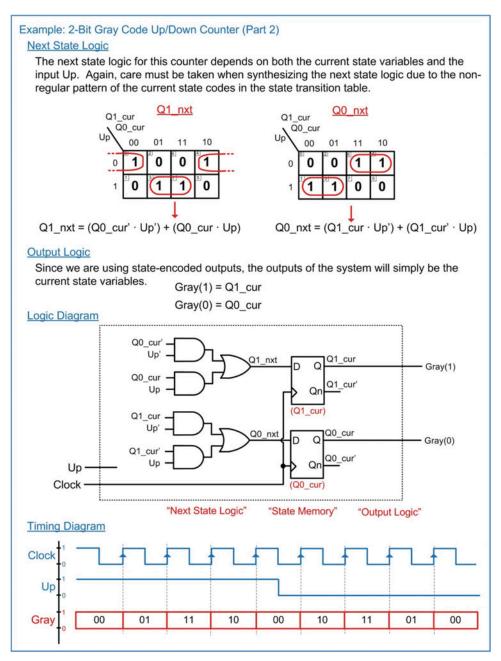

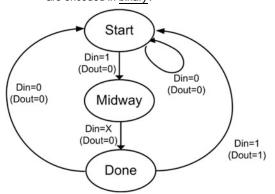

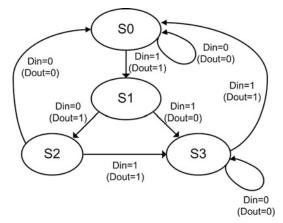

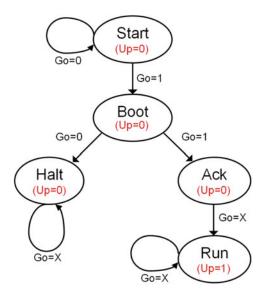

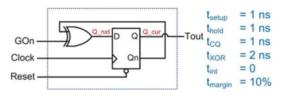

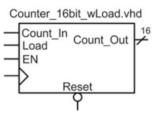

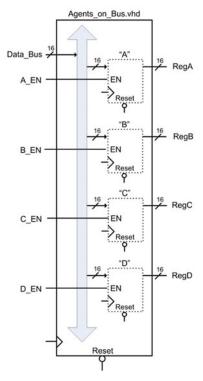

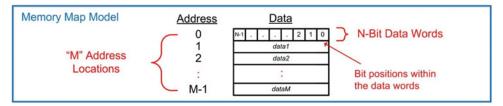

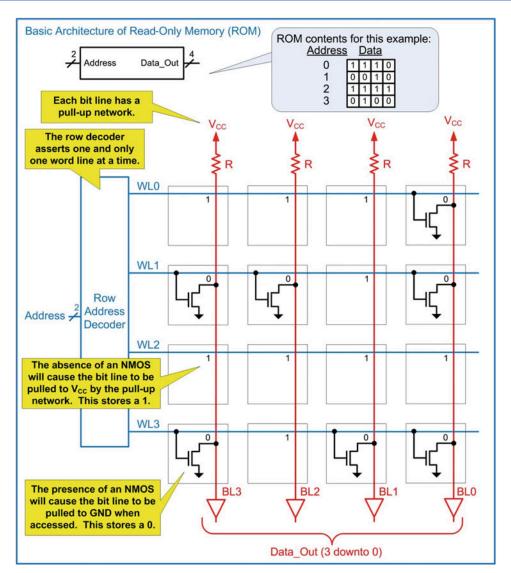

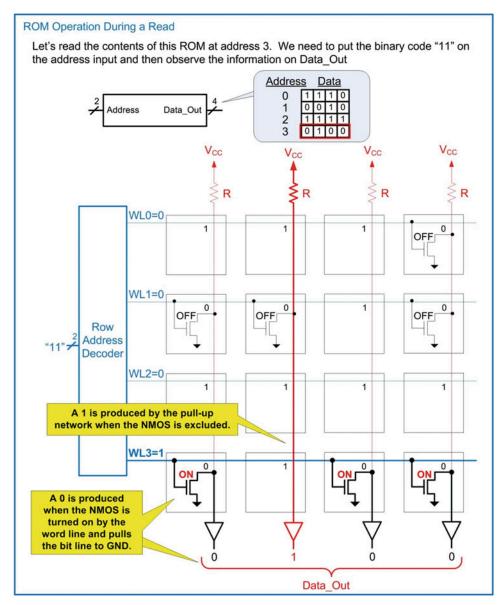

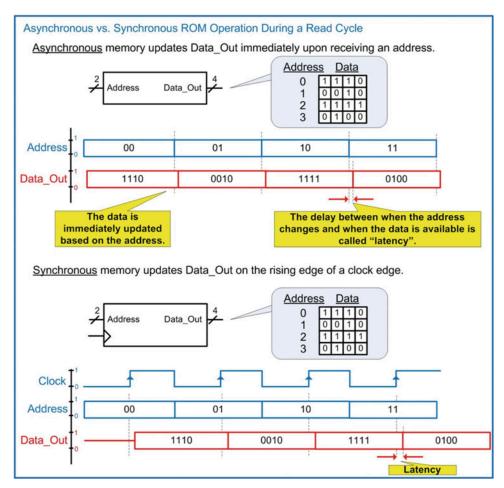

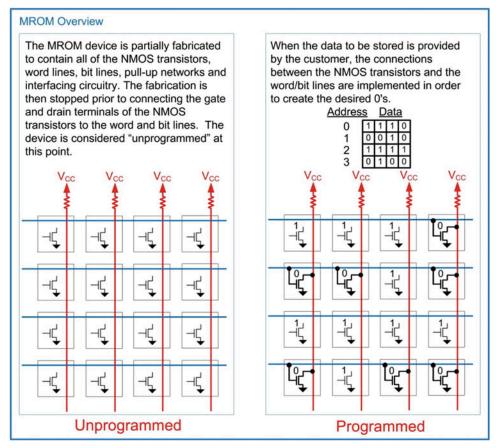

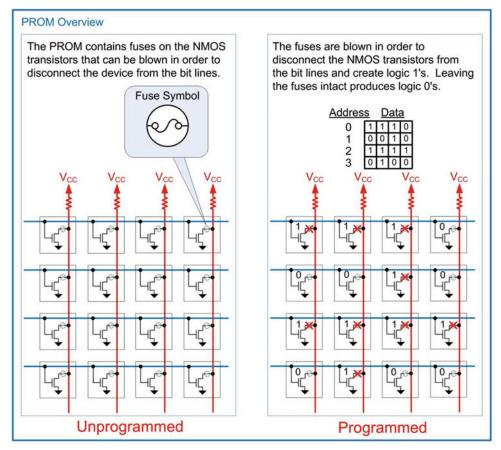

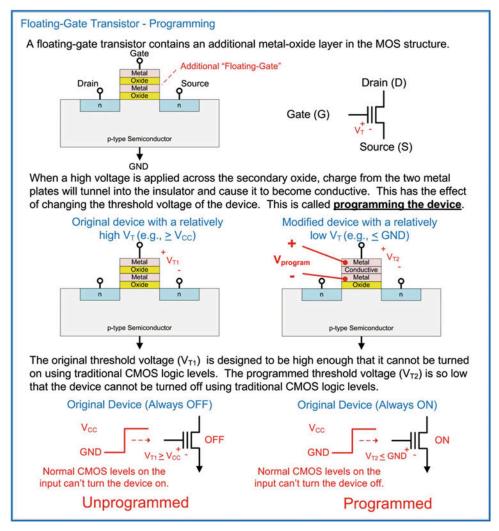

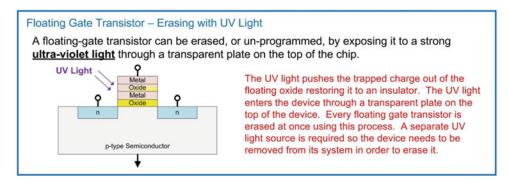

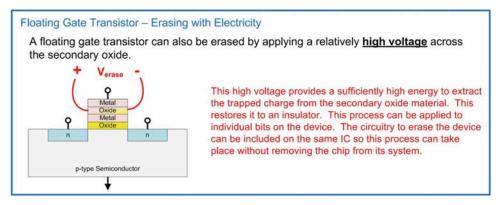

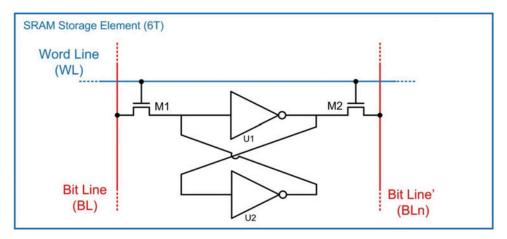

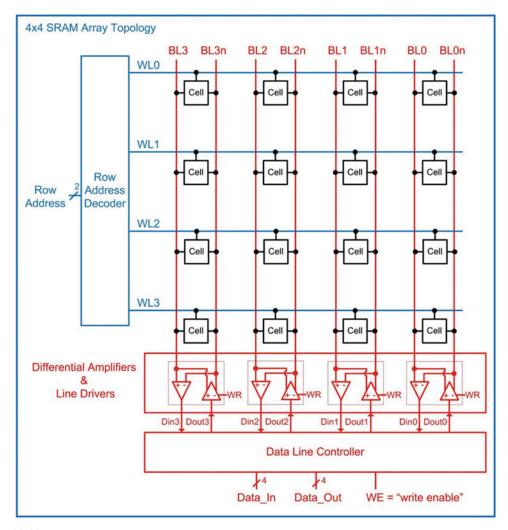

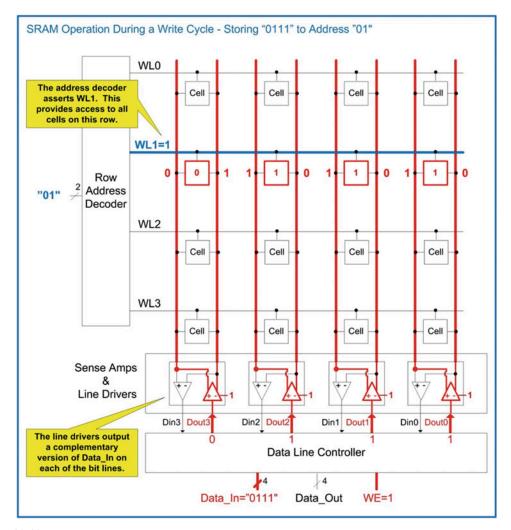

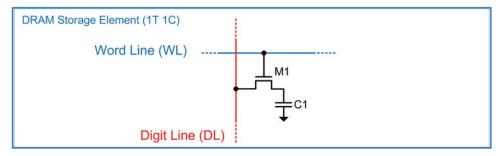

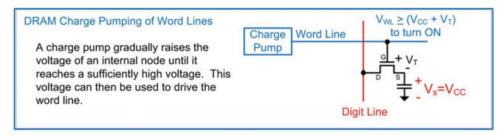

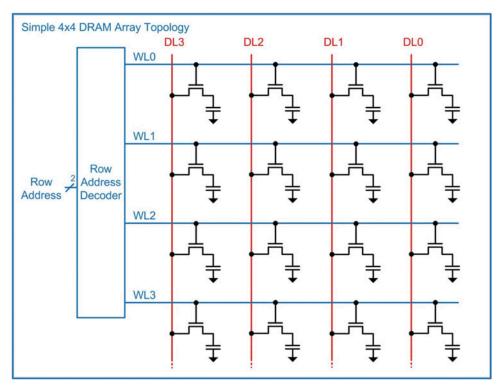

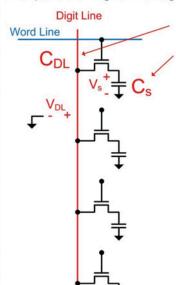

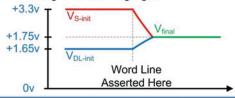

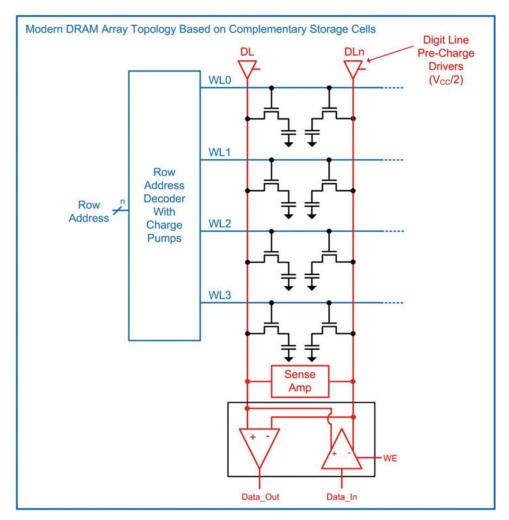

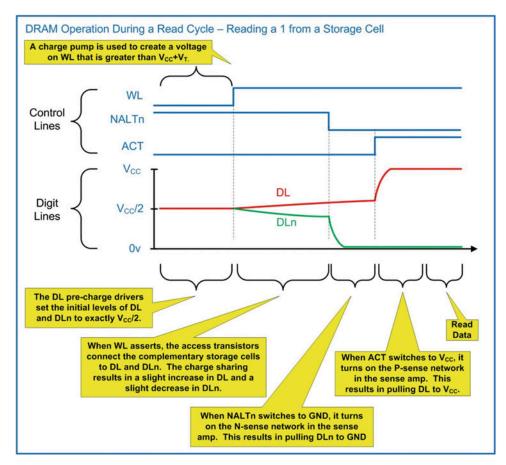

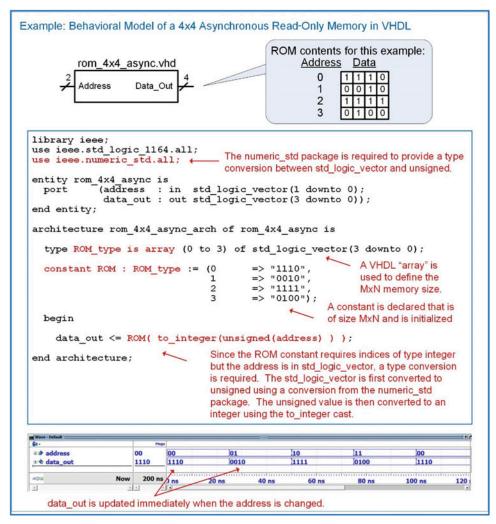

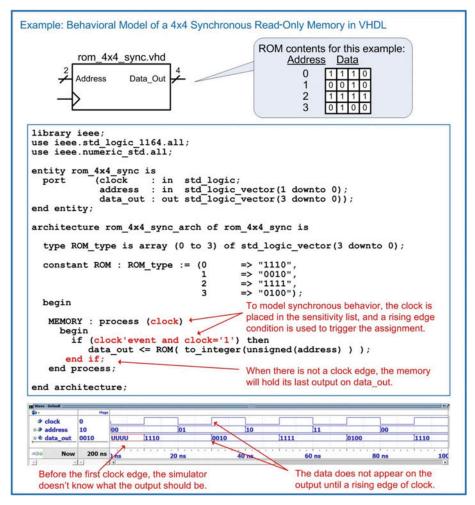

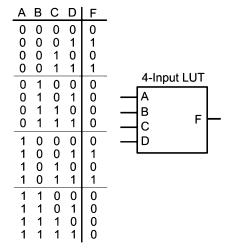

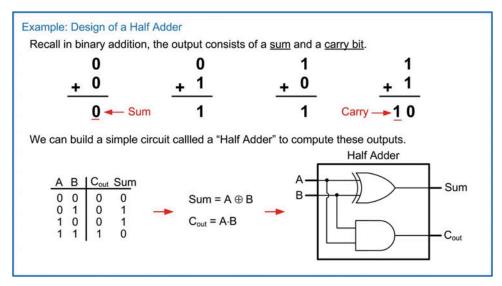

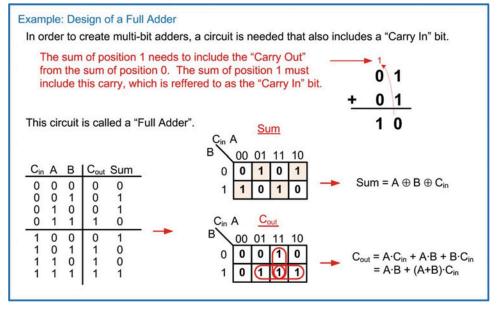

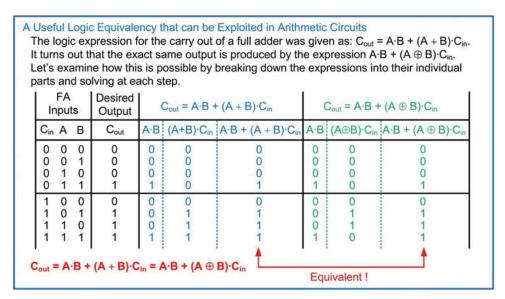

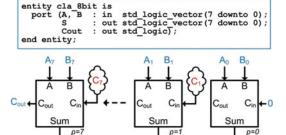

#### 2.2.3.3 Octal to Binary